### 3次元 LSI 実装のための TSV 技術の研究開発動向

LSI 製造プロセスの微細化がもたらす高集積化によって、コンピュータを始めとした 電子機器はこれまで、小型化、多機能化、高速化などの高性能化を果たしてきた。この 微細化には技術的な限界が見えてきており、この限界を打開する技術として、シリコン 貫通電極(TSV)を用いた3次元実装技術(TSV技術と呼ぶ)に期待が寄せられている。 TSV 技術は、従来の微細化の追求に代わる実装技術のひとつとして注目されているが、 さらに、複数の異種 LSI チップや MEMS を混載して多機能 LSI を実現できる点でも、 期待が寄せられている技術である。

我が国では、他国に先行して TSV 技術の実用化研究が行われ、製品化でも先行してき たが、これらの事例はまだ TSV 技術の小規模適用にすぎず、適用のメリットも小型化と 高密度化を主としたものである。現在は、動作の高速化、省エネ化、多機能・高機能化 など、TSV 技術の複数のメリットを最大限に生かした、より高度な TSV 技術の実用化 を目指して、設計手法の見直しにまで及ぶような研究・開発が世界中で行われている。 一方で、TSV を形成するための基本製造技術、TSV 技術を適用するための周辺技術、 および、TSV 技術を高度に利用するための設計技術など、解決すべき課題は広範にわたっ ている。

世界各国は、TSV 技術の実用化を見据えた研究プロジェクトを開始するなどの対応を 図っているが、各国のプロジェクトを概観すると、TSV 技術の基本技術とその応用の研 究開発に余念のない米国の拠点、EDA (Electronic Design Automation、設計自動化) ツー ルの新規開発と技術適用の将来展望を持って TSV 技術の実用化にも力を入れている欧州 の拠点、基礎技術を有しながら TSV 技術適用の実用試作に注力している欧米韓連合のコ ンソーシアム、周辺技術などを抑えて実用化に取り組む日本のコンソーシアム、という 違いが窺える。

これらは総じてグローバルな連携を志向した動きであり、最先端の LSI 開発技術の進 め方として、グローバルな連携というキーワードは注目していく必要があろう。

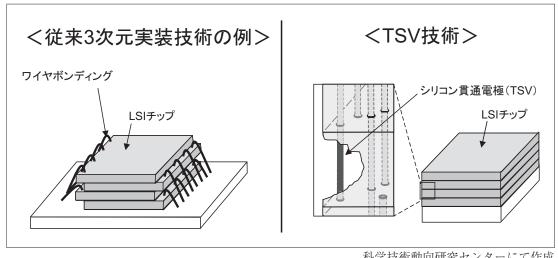

#### 従来の3次元実装技術とTSV技術

科学技術動向研究センターにて作成

### 科学技術動向研究

# 3次元 LSI 実装のための TSV 技術の研究開発動向

**吉永 孝司** 情報通信ユニット

野村

稔

客員研究官

## / はじめに

LSI 製造プロセスの微細化がもンピュータを始めとした電子機器によって機器化、コータを始めとした電子機器による機能化、る機能化、る機能化を果たしの高性能化を果たしの発熱を伴うリーク電流の増大や、思題とながはる信号遅延などが課題となって、はおける信号なる微細化へ平面の微細化限界を打開するに、平面の微細化限界を打開するにでひず高集積化をはかることが形式といたよいたよいたよいたようで表現されていたLSI

チップを縦方向に積層することで、 そのLSIが有していた機能を変え ることなく、実装面積を減らした LSI部品を作ることができる。

この3次元実装の開発の鍵は、 積層されたLSIチップ間の電気信 号をいかに接続するか、という電 気的な実装技術にある。これまで の主要な実装技術は金属細線を 使ったワイヤボンディングであっ たが、近年になり、この有線接続 に代わる接続方法の研究が進めら れている。そのひとつは、ワイヤ ボンディングの配線スペースを無 くし、無線でデータ通信を行う接 続方法の提案である $^{1-4)}$ 。また、同様にワイヤボンディングの配線スペースを無くし、より短い配線で有線接続する方法として、シリコン貫通電極(TSV: Through-silicon via)を使った実装技術(以下、TSV技術と呼ぶ)が研究されている $^{5-7)}$ 。TSV技術は、これらの3次元実装技術の中で、実用化において他に先行している $^{8.9)}$ 。

ここでは、3次元実装技術の中でTSV技術を取り上げ、技術の特徴を紹介し、実現に必要な技術課題とそれを支える研究体制について述べる。

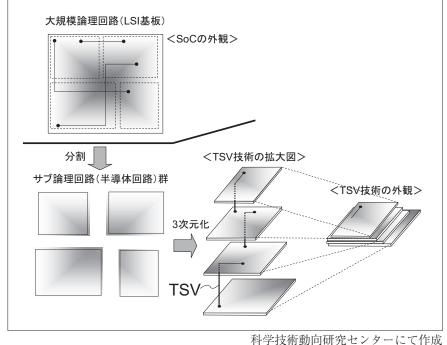

図表1 従来の3次元実装技術と TSV 技術

科学技術動向研究センターにて作成

### )シリコン貫通電極 (TSV) 技術とは

### 2-1

### 3 次元実装技術の中の TSV 技術

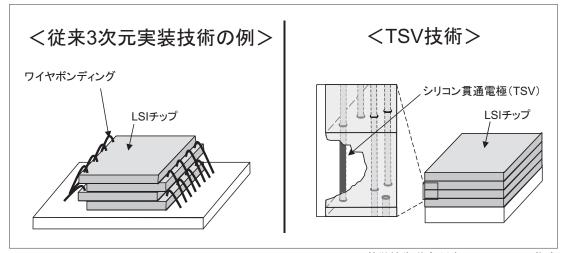

3次元実装は実装密度を高める 技術として、これまで、ワイヤボ ンディングなどを用いた電気接続 による実装が行われてきた。3次 元実装技術のさらに進んだ姿とし て、より実装密度を高めた TSV 技 術がある(図表 2)。

TSV 技術とは、LSI チップを積層し、この LSI チップを貫通する縦配線となるシリコン貫通電極 (TSV)を用いて LSI チップ相互間の回路接続を行い(図表1)、1つの LSI 部品として外装ケース (package)に実装する技術である。 TSV 技術は、従来の微細化の追求に代わる実装技術のひとつとして注目されているが、さらに、複数の異種 LSI チップや MEMS を混載して多機能 LSI を実現できる点

でも、期待が寄せられている技術である。

我が国では、1998年当時の通商 産業省の支援で発足した実装技術 研究プロジェクトとして、技術研 究組合 超先端電子技術開発機構 (ASET)が主体となり、3次元高密 度集積化技術としての TSV 技術の 開発が他国に先行して始められ た 10)。 産業界では、2007 年に(株) 東芝が携帯電話など向けのカメラ モジュールに、世界で初めて TSV ((株)東芝では TCV: Through Chip Via と呼んでいた)技術を採用して 64%のサイズダウンを果たし話題 を呼んだ<sup>8)</sup>。その後、エルピーダ メモリ(株)が8枚のLSIメモリチッ プを積層してメモリ容量を8倍に した DRAM 開発の完了を報告し ている 9)。

このように、近年になって TSV 技術の実用化に関する発表が相次いでいるが、これらの事例はまだ TSV 技術の小規模適用にすぎず、適用のメリットも小型化と高密度

化を主としたものである。現在は、TSV 技術の複数のメリットを最大限に生かした、より高度な TSV 技術の実用化を目指して、設計手法の見直しにまで及ぶような研究・開発が世界中で行われている。

### 2-2

### 二つの方向性から見る TSV 技術

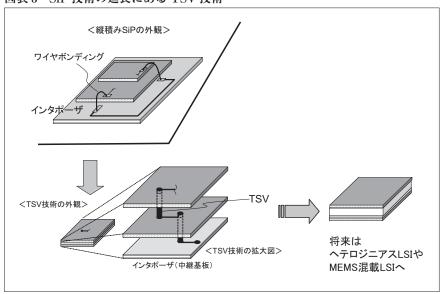

LSIの小型・高密度化の手法は、 SiP (System in package)と呼ばれ る実装技術を使う手法と、LSIの 設計手法である SoC (System on a chip)を利用する方法の2つに大別 される。SiP技術は、それぞれ個 別に製造された LSI チップを複数 個組み合わせ、それを1つの外装 ケースに実装して外部接続端子を 付け、1つのLSI部品として完成 させる実装技術である。一方、 SoCは、機能回路ブロックなどを 含む論理回路を LSI チップ内に集 積して1つのLSI 部品にまとめあ げるという、LSIの設計手法であ る。 以下、TSV 技術を、これら2 つの方向性から説明する。

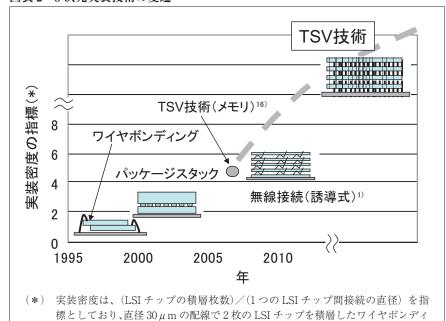

# (1) SiP 技術の延長にあるTSV 技術

SiP技術は、複数のLSI間をワイヤなどで接続する技術を基本技術としている。3次元実装技術におけるSiP技術は、デジタルカメラや携帯電話などの小型・高密度実装において多用されている。図表3はSiP技術の延長にあるTSV技術を示している。SiP技術では、異なる機能を持つLSIチップを縦積みや横置きにし、インタポーザ(LSIチップの配線を接続するための中継基板)を使って、ワイヤボン

図表 2 3 次元実装技術の変遷

ングの場合を「1」として正規化している。

科学技術動向研究センターにて作成

ディングなどでLSIチップ間を電 気的に相互接続し、1つのLSI部 品として完成させている(図表3左 上)。これに対して、異なる機能の LSI チップを縦積みし、LSI チップ 間を、ワイヤボンディングの代わ りに TSV で電気接続する 3 次元実 装技術が TSV 技術である。2-1 項 のカメラモジュールやメモリ積層 の例はこの方向性にあり、さらに 高密度化させる将来の技術として、 異種のLSIチップの混載(ヘテロジ ニアス LSI)、あるいは LSI チップ とMEMSなどを混載したISI部 品への応用が考えられる。

### (2) SoC の発想転換による TSV 技術

図表4は、もともと2次元の設 計手法であった SoC を 3 次元に発 想転換し、3次元実装を実現する 例を説明している。2次元平面に おいて1つのLSIチップでできて いた論理回路をサブ論理回路群に 分割し、2次元レイアウトから3 次元レイアウトに変えるという発

想である。2次元面積を減らして 同等の機能を実現できるというこ とで、小型・高密度化に関して、 LSIの微細化と同等の効果が得ら れる。このような実例はまだ現れ ていないが、高密度実装のロジッ ク LSI 部品などで実現するだろう と考えられる。

### 2-3

### TSV 技術を適用するメリット

以下に、TSV 技術を適用するこ とで得られるメリットを、従来の 実装技術との対比で示す。

### (1) 小型化・高密度化

図表3および図表4に例示した ように、TSV 技術を使うと、まず LSI 部品を小型化できる。SiP 技術 でも縦積み実装は行われてきたが、 LSIチップの外側へ張り出したワ イヤボンディングをなくせること で、さらに小型化できる。また、 「SoC の発想転換」という方向性で は、平面での構成から縦積み実装 に変えることで、1つのLSIの面 積を数分の一程度に小型化できる。 一方、高密度化という意味では、 例えば CPU 内の多数のプロセッ サ・コア回路を多段実装して、並 列処理プロセッサ(many core processor) の LSI 部品として実現 する技術などに有効に使えるとの 報告がある。

### (2) 信号伝送と処理速度の 高速化

図表3および図表4に例示した ように、2次元実装で長くなる配 線の全長を、TSV 技術を使うこと で短くできる。配線が短いと信号 は速く伝わり、遅延の原因となる 配線相互の干渉も少なくなるため、 伝送速度の高速化を図ることがで きる。また、高速のデータ伝送を 繰り返すLSIチップを縦積みし、

図表3 SiP 技術の延長にある TSV 技術

科学技術動向研究センターにて作成

図表 4 SoC の発想転換による TSV 技術

科学技術動向研究センターにて作成

その間の接続をTSVで行うと、LSIチップのレイアウトの自由度が高まり、配線長を短くでき、高速化を図ることができる。これをスーパーコンピュータ用のLSIに適用し、演算部とメモリ間のデータ転送を高速化すると、現行機比で44%の高速化が実現できることが数値計算で示されている<sup>11)</sup>。

### (3) 省エネルギー化

配線の電気抵抗は発熱の原因に なる。また、配線の量や長さに依 存して配線の浮遊容量が増加し、 配線への充放電電流が増えること も発熱の原因になる。TSV 技術で 電気配線長を短くできると、これ らのエネルギー損失を減らすこと ができる。また、損失による信号 減衰や遅延が原因で必要となって いた配線途中へのリピータ(信号中 継素子)の挿入数も削減でき、その 電力を減らすことができる。(2)で 挙げたスーパーコンピュータ用 LSIへの適用例では、14%の省エ ネルギー化を実現できると試算さ れている11)。

### (4) 多端子化

TSV 技術によって、多端子化も 実現できる。従来、SiP技術にお けるワイヤボンディングは、チッ プの周囲に配置されるため、チッ プの周辺からだけしか端子が引き 出せなかったが、TSV 技術を用い た場合は、LSIチップの任意の位 置に端子を設けられる(図表1)。 端子に接続できるインタフェース の数が増え、端子位置の制限が減 ることで、LSIチップ間接続の設 計自由度が高まるとともに、回路 レイアウトの自由度も高められる。 さらに、端子から出る配線数を増 やせることで、LSI チップ間のデー タの並列伝送数を増やすことがで き、データ転送の高速化にも寄与 する。

### (5) 多機能化による高機能化

従来から SiP 技術を使った多機 能化が図られてきたが、TSV 技術 を使って多端子化のメリットを生 かせば、より多くの LSI チップ機 能を1つの外装ケースに収容でき る。具体例として、多数のメモリ チップと多数の高速プロセッサ チップ、それに多数のイメージセンサを TSV 技術で多端子接続して 実装し並列処理できるようにし、 高速化および小型化のメリットも 活用すれば、毎秒1万フレームの 高解像度・高速イメージセンサが、 1つの外装ケースに収容できる <sup>12)</sup>。 このように、従来にはない高機能 化を実現できる。

### 2-4

### TSV 技術の適用分野

配線の微細化が進んだLSIには、 それに見合うように、より細い径 のTSVが要求され、回路規模が大 きくなるLSIには、より多くの TSV 本数が要求されるようにな る。

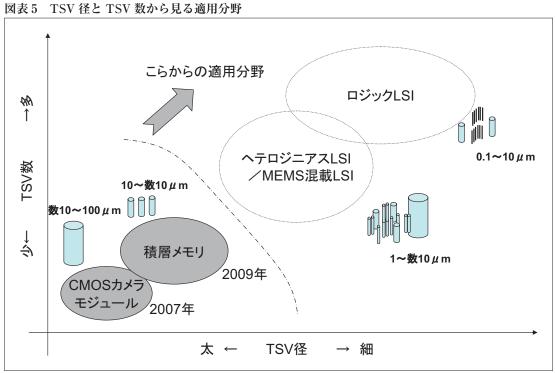

図表5は、横軸にTSV径の太さを、そして縦軸にTSV数を示し、この2軸上の該当箇所に適用分野、あるいは製品を位置づけたものである。

例えば、すでに発表されたカメ ラモジュールの TSV 技術は、TSV

科学技術動向研究センターにて作成

数も少なく、TSV 径も太い。同じく発表済みのメモリ積層では TSV 数も増え、TSV 径も細くなっているが、TSV 数はまだ数千本単位に留まっていた。しかし、これから開発されると考えられるロジック LSI 部品などでは、さらに小径の TSV を数万本単位に増やしていくことが必要になってくる。スペースという意味では、仮に TSV 径を  $1~\mu$ m とすれば、1mm 四方のなかに、TSV を 100 万本まで形成でき

る。ただし、LSI 部品内で使われる TSV 径は、1 種類ではないこともある。ロジック LSI などでは、小径の TSV が適用される信号系と、電流容量を確保するために太い TSV が必要な電源系とが混在する。また、異種の LSI チップを混載するヘテロジニアス LSI やME M S 混載の LSI 部品でも、さらに様々な径の TSV が適用されるであろう。

したがって、ひとくくりに TSV

技術といっても、その適用分野に よって、TSV の形成技術の難度は 大きく変わってくる。

### 2-5

### TSV 技術を実現する工程

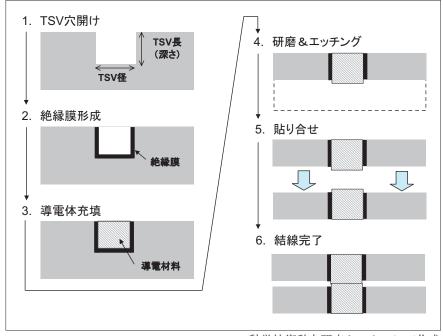

TSV 技術を実現する工程は、シリコン基板(LSI チップが作られる基板)に TSV を形成する工程と、これらの LSI チップを貼り合わせ、TSV を介して LSI チップ内の電気配線を接続する工程から成る。

まずは、シリコン基板に穴を開け(図表6の1.)、シリコン基板とTSVとの干渉を避ける絶縁膜を形成し(同図の2.)、導電体を充填して(同図の3.)、TSVが完成する。次にTSV相互の接続を行うため、TSVが設けられたシリコン基板を研磨で薄く加工し、TSVを残すようにエッチング処理(不要部分を除去)することで、TSVを露出させる(同図の4.)。最後に、LSIチップを貼り合わせ(同図の5.)てTSV相互をつなぎ合わせることで、TSVを介した2つのLSIチップ間の配線接続が完了する(同図の6.)。

図表 6 TSV 技術を実現する工程 (断面図)

科学技術動向研究センターにて作成

# 子 TSV 技術に関わる研究開発課題

### 3-1

### 製造に関わる主な技術課題

#### (1) TSV の穴開け技術

製造に関わる技術課題の中で、 まず挙げられる大きな課題は、 TSV を貫通させるための穴を、シ リコン基板に開ける技術にある。

TSV の穴開け技術は、アスペクト比(TSV の長さ/TSV 径)が数倍から数十倍になるような、小径で

深い穴を開けるとうい難しい技術である。穴径が小さく、また、アスペクト比が高いほど難度は増し、アスペクト比が高いほど加工時間(穴開け処理時間)も長くなる。どのようなプロセスをどう使うのか、TSV径、TSV長をどう決定するかなどの試行錯誤が繰り返される。

TSV 穴開け手法としては、ME MSの加工技術として開発された 深掘りプロセスである「Bosch プロセス」 <sup>13)</sup> と呼ばれる方法と、Bosch プロセスではないという意味で 「non-Bosch プロセス」と呼ばれる 方法がある。Bosch プロセスとは、 ドイツ Bosch 社が開発した穴開け 方法であり、反応性イオンエッチ ングで浅い穴を掘り、次に絶縁 を作り、また穴を掘り進める処理 を繰り返すことでで垂直に深いに性 を繰り返すことである。反応性イオンエッチング(Reactive Ion Etching, RIE)とは、反応性のあるせで (エッチングガス)を充満させてプラ で電磁波を照射することを 第マを発生させ、試料に電位を与 えることでイオンやラジカルをぶつけて穴を開ける技術である<sup>14</sup>。

一方、non-Bosch プロセスは、 プラズマエッチングの制御方法を 工夫することで、エッチング方向 に異方性を持たせ、結果として、 Bosch プロセスで必要な絶縁膜形成の処理を穴開けの途中で行わず に深掘りを可能にした方法である。

このようにして開けた穴の内壁に絶縁膜を形成し、次いで導電体を充填することになるが、導電体として使われる材料は TSV を形成する工程により影響を受けるため、後述の(4)でまとめて説明することとし、次に、研磨とエッチングについて説明する。

#### (2) 研磨とエッチング技術

TSV 用の穴を開けるには長時間 を要することから、TSV 長が短く てもよいようにするため、研磨に よってシリコン基板を数百μmか ら数十μm程度に薄くする。さら に、電極となる導電体を露出させ るために、シリコン基板のエッチ ング処理を行う。積層時の厚さ方 向の実装密度を高め、完成した LSI部品を薄く仕上げるためにも、 シリコン基板を薄くすることは有 効である。ただし、研磨する際に は機械的なストレスがシリコン基 板にかかる為、シリコン基板にガ ラス基板を貼り合わせて堅固にし た上で一連の処理を行うなどの配 慮が必要になる。また、この処理 が終了すると、このガラス基板を 取り外すなどの処理を必要とする。 この研磨の手順をどうするか、研 磨によって発生する粉じんの処理 をどうするかといった課題のほか にも、この貼り付けの接着剤をど うするか、どのようにガラス基板 を剥離するかなどの研究が行われ ている。

#### (3) 接続技術

TSV 相互の接続技術には、LSI チップを切り出す前のシリコン基 板(ウェハー)単位で貼り合わせる 方法(Wafer to Wafer)、ウェハー から切り出した LSI チップ(ダイ) をウェハーに貼り合わせる方法 (Die to Wafer)、切り出したLSI チップ同士を貼り合わせる方法 (Die to Die)がある。この貼り合わ せ方法も、技術の難易度やコスト の両面で一長一短があり、そのプ ロセスが研究の対象になっている。 この貼り合わせの際に、ウェハー 単位で貼り合わせる場合には、例 えば直径300mmの円盤状のウェ ハーで、その上にある LSI チップ 毎に数千から数万点に及ぶ直径 1μmの TSV がすべて正確に重な るような位置合わせを行うため、 高度な位置合わせ技術が必要にな る。接続技術には、LSIの回路を 向き合わせて貼り合わせる方法 (Face to Face)と、LSI を同方向に 縦積みにして貼り合わせ方法 (Face to Back) があり、このLSI チップの向きの違いによっても異 なる貼り合わせ技術の研究が必要 になる。

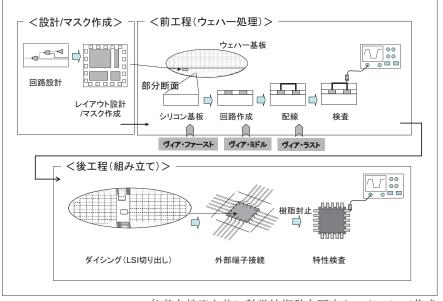

#### (4) TSV 形成のタイミング

製造工程のどの段階でTSVを形成するかというタイミングにより、3つのプロセスがある。図表7に

は一般的な LSI の製造工程を示し た<sup>15)</sup>、この工程に当てはめて、こ の3つのプロセスを説明する。1 つめはヴィア・ファースト(vias first)と呼ばれ、回路作成前のシリ コン基板の状態で TSV を形成する 方法である。2つめのヴィア・ミ ドル(vias middle)は、回路作成が 終わり回路間の配線がなされる前 に TSV を形成する。分類によって はこのヴィア・ミドルまでをヴィ ア・ファーストに含めている場合 もある。3つめのヴィア・ラスト (vias last) は、配線が終わったあと に TSV を形成する。LSI チップを 重ねたあとでチップ間を貫通する TSV を形成する場合もヴィア・ラ ストと呼び、図表7の後工程に位 置する。

これらのタイミングの違いにより、TSVに充填する材料も異なる。電気配線である TSV には導電体を用いるが、ヴィア・ファーストやヴィア・ミドルでは、高熱に耐え、工程への親和性が高いポリシリコンが、ヴィア・ラストでは使用する材料制限が緩くなり、Cu(銅)、W(タングステン)、Al(アルミニウム)が使われる<sup>16)</sup>。充填材料に求められる電気特性としては低抵抗(高電気伝導率)が求められるが、

図表 7 LSI の一般的な製造工程における TSV 形成のタイミング

参考文献 15) を基に科学技術動向研究センターにて作成

ポリシリコンは抵抗値が高く、Cu、Alは抵抗値が低い。その為、ポリシリコンを嫌い、Ni(ニッケル)を使う検討もされている。

TSV 製造の最良タイミングもまだ定まっておらず、研究対象となっている。

### 3-2

### 複雑化かつ高度化する 周辺技術課題

以下は、従来のLSI製造技術においても課題であったが、TSV技術を適用するにあたり、さらに複雑化、かつ高度化する技術課題である。

### (1) テスト技術

TSV 技術を使って多数の LSI チップや MEMS を多段実装する と、内層に位置する LSI チップや MEMS の動作テスト用端子(イン タフェース端子)は、完成したLSI 部品の外部に露出しない場合が出 てくる。この場合には、内層の LSI チップや MEMS の動作テスト は、すべて、外部に露出した端子 からしか行えないため、インタ フェースは制限され、その結果、 テスト項目は複雑化し、テストに は長時間を要してしまう。よって、 効率よく動作テストを実施するた めの方策として、例えばテスト項 目を絞り込むテストプログラムの 開発や、高速のデータ取得、解析 手法の研究が必要になってくる。

また、この外部端子における動作テストで不合格になるということは、多数のLSIチップやMEMSが不良品になり、損失を大きくすることを意味する。よって、従来に増して、LSIチップ単位で良品の判別テストが重要になる。

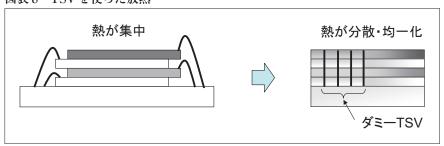

### (2) 熱設計技術および放熱 処理技術

一般に、LSIが動作すると発熱 し、LSIチップ自体の動作環境温 度を上げてしまう。高温環境下で の動作は LSI チップの信頼性を低 下させるため、信頼性確保のため には熱設計と放熱処理が重要にな る。特に縦積み実装の場合には、 積層の内部に挟まれるチップの熱 設計が難しくなる。また、LSIチッ プの発熱に分布差が生じると、熱 膨張の違いによる機械的なひずみ が生じて TSV 接続箇所に過度の負 荷がかかるなど、これも LSI 部品 の信頼性を低下させる要因になる ため、熱設計による対処が要求さ れる。一方で、図表8に示すよう に、ダミーの TSV を形成し、TSV の熱伝導を積極的に利用して熱の 拡散や放熱に使おうという考えも ある 17)。

また、発熱の大きいLSIチップを多段積層する場合には、さらに踏み込んだ熱設計が必要になる。例えば、前述した技術研究組合のASETでは、ハイエンドのLSI部品の水冷技術について、LSIチップ間に冷却水を流す実験が行われてきた5。また、IBM社でも、冷却液を使ったオリジナルな冷却技

術を研究する動きがある。

熱設計のためには、レイアウト設計段階での熱シミュレーションや、熱による機械的な歪みを考慮した構造解析も必要になるが、これらを統合化して、電気設計と熱、構造などの協調設計の研究も必要になってくる $^{12}$ 。

### (3) 信号品質および電源品質 の解析技術

TSV 技術を組み込んだ LSI 部品では、従来に無かった縦配線となる電極が新たに加わる。従って、この TSV の導電素材・周囲の絶縁材・貫通するシリコン基板の物理特性を考慮して TSV の信号伝送に関連する電気・電磁特性を設計しなければならない。また、回路シミュレータを使った信号品質(SI: Signal Integrity という)の解析を行うための TSV の部品モデル、すなわち擬似電気回路網の作成も研究対象である。このモデル作成には、回路シミュレータと電磁界シミュレータの連携が欠かせない。

また、従来のノウハウを生かしながら what if 解析、すなわち仮説、仮定に基づくパラメータ変更解析を行うことも必要になり、シミュレータの高速化が求められる。

一方、LSIの安定動作のために、 直流的には電圧降下が少なく、交 流的には電圧変動が少ないことが 求められる。これを、電源品質(PI: Power Integrity という)が良いと いう。

直流的な電圧降下に関しては、TSV 径の太さやTSV の充填に用いる導電体の直流抵抗値などがパラメータになる。また、交流的な変動は、キャパシタンス(静電容量)とインダクタンス(誘導係数)がパラメータとなる。特に高周波の変動を低減する部品としてキャパシタ(コンデンサ)が使われるが、キャパシタの効果を十分に生かすためにはLSIチップの直近に配置することが有効であるため、LSIチッ

図表 8 TSV を使った放熱

科学技術動向研究センターにて作成

プの中にキャパシタを設けたり、 インタポーザの中にキャパシタを 埋め込んだりする技術が求められ る。

#### (4) 電磁干渉回避

# (EMC:Electromagnetic Compatibility) 技術

直接に配線されていない回路間 であっても、電磁結合による相互 の干渉により、互いの回路動作に 影響を及ぼす場合がある。TSV 技 術では、LSI チップや MEMS の混 載により、様々な電圧・周波数の 信号が交錯し、かつ、LSIチップ 間は数十µm、TSV間は数µmに まで配線が近接することから、配 線間の電磁干渉が無視できなく なってくる。また、電磁干渉を低 減させるひとつの有効な手段は、 回路の近くに、面積が広く、電位 の安定した基準電位(グラウンド) を設けることであるが、TSV 技術 では多段積層になることで、全て の回路に共通する基準電位の配置 が難しくなる。

さらに、電磁ノイズ放出の低減に関する研究も重要となる。上記の電磁干渉が外部の機器の動作や通信に影響を与えることがあるため、電磁ノイズ放出の上限値が国際規格で決められ、我が国でも放出規制を行っている<sup>18)</sup>。TSV技術により LSI 部品が高密度化し、高機能化・大規模化すると、これらの電磁ノイズ放出抑制に対する対処法も複雑化してくる。

ここでも、SIやPIの設計に使われるシミュレーション技術が重用される。

### 3-3

### TSV 技術の設計に関わる技術

LSIの製造工程は、設計工程・ 前工程・後工程に分けられるが(図 表7)、その冒頭にあるのが設計工 程である。設計工程は、システム 設計・論理設計・レイアウト設計・ テスト設計などの各設計項目に分 けられる。また、近年では設計と 製造は緊密に連携していることか ら、製造方法の決定も、設計技術 の一部とみなす。この設計工程全 体を通して、電気的、機械的な条 件・制約の中で、製造の最適化を 図りながら製品化するための技術 が、設計技術である。設計技術は、 設計思想(アーキテクチャー)に 基づき、EDA (Electronic Design Automation、設計自動化)ツール などの設計支援ソフトウェアツー ルを使うことで実現される。この うち、TSV 技術を導入するにあ たって、設計工程で主に考えなけ ればならないのは、以下の2点で ある。

### (1) TSV 技術特有の設計技術

2-3 項で述べたように、TSV 技 術を使った3次元実装技術は、設 計の自由度を大きく高める。言い 換えれば、設計の良し悪しにより 完成する LSI 部品の性能が大きく 変動する可能性を有していること になる。具体的には、TSV 技術の 適用によって、LSIチップやLSI 部品のレイアウト設計に大きな影 響を与えるということになる。レ イアウト設計とは、回路部品の配 置とその間の配線を行い、LSIチッ プの製造で使用するマスクデータ を作成する作業である。特に、大 規模ロジック LSI 部品の設計を行 う場合には、全体最適となる各配 線長を考慮して、TSV の位置を決 定する必要がある。この際、性能 のよい LSI 部品を効率よく設計す るには、新たなEDAツール開発 を伴う新しい設計技術の開発が必 要になる。

また、SiP技術では入出力(I/O) 回路を備えたパッドを介して外部への配線を行っているが、TSV技

術では、I/O 回路を介さない LSI チップ内の回路間接続も可能になる。それ故、回路間の接続にあたっては、I/O 回路が担っていた波形整形も考慮した対策も必要となる。さらに言えば、よい設計を効率よく行うためには専用の設計ツールが必要になるということである。

# (2) 各企業が競争優位を保つ ための設計技術

TSV 技術のコアとなる技術は、 TSV 形成のための製造装置を用い ることを基本とするが、各種のコ ア技術の最適な組み合わせはまだ 決まっていない。製品化にあたっ ては、それぞれの半導体メーカー がこれらの技術を選択して独自の 組み合わせを行い、製造装置のパ ラメータ設定などのノウハウを生 かすことで、他社に対して競争優 位を保つ開発を行うことになる。 この開発においては、製造性、製 品性、信頼性、コストなどを総合 的に判断して LSI 部品全体の設計 を決める必要がある。その重要な 技術要素は前項にも列挙したが、 忘れてはいけないのが「コスト」で ある。SiP 技術の例では、小型化、 高密度化、多機能化については、 すでにワイヤボンディングでの製 品化の実績がある。TSV 技術の設 計技術はワイヤボンディングを 使った製品とのコスト比較が重要 な設計要素となる。デバイス技術 者が許容範囲とする TSV 採用によ るコスト上昇の水準は、300mm ウェハー1枚あたりで200米ドル とされている。しかし将来的には これを50米ドルに下げるとの目標 が示されている <sup>19)</sup>。これを達成す る見込みのある日本のベンチャー 発の製造技術も発表されている<sup>20)</sup>。 このような技術の取り込み、自社 向けへのアレンジなどの積み上げ が、競争優位を保つ戦略につなが ると考えられる。

# 4

### TSV 技術に関連する研究体制の具体例

3章で述べた各種研究課題の解決に向けて、現在、世界中で様々な研究開発が行われている。図表9は、TSV技術に関わる研究を行っている、半導体の設計や製造、およびナノ加工などの代表的な研究機関である。本章では、これらの拠点で行われているTSV技術の実用化を見据えた実行プロジェクトを抜粋し、それぞれの特徴を示す。

### 4-1

# 米国 SEMATECH (Semiconductor Manufacturing Technology Institute)

米 国 SEMATECH で は、TSV 技術開発のプログラム「3D Interconnect」を 2007 年 3 月に立ち上げ ており、協業の参加者を呼び掛け ている。その協業のターゲットは 「area of basic, precompetitive R&D」、つまり、産業上の非競争 分野であるとされている。このプロジェクトには以下の特徴があ る<sup>21、22)</sup>。

#### (1)参加メンバーの多様性

参加メンバーの対象は世界中に 広がっており、半導体販売社、チッ プメーカー、材料メーカー、組み 立て&パッケージング会社に加え、 設計、テスト、半導体製造装置など、 全半導体産業分野にわたる。

#### (2)現場志向のアプローチ

TSV 技術の課題解決手段として、①3D 実装の方法、製造方法、使用ツールなどの業界コンセンサスを得ること、②製造フローのコストや製品に依存した知識を増やすこと、③特定の完成した製造方法を開発すること、④ロードマップ作成と標準化作業を行うことが挙げられており、現場志向のプログラムが組まれている。

#### (3) その他の特徴

本プログラムの参加促進策としては、SEMATECHが有する新しい製造技術が使えることが挙げられる。このプログラムとは別に、SEMATECHは、LSI製造装置メーカーである東京エレクトロン(株)と密接な協力関係にあり<sup>23、24</sup>、TSV

形成のためのエッチング装置の開発においても連携している。半導体製造装置メーカーとの連携強化は、特に「前工程」(図表7)と呼ばれる半導体製造工程の技術力強化につながっている。SEMATECHは前工程分野で、CNSE(College of Nanoscale Science and Engineering)のような大学との共同研究も行っている。

### 4-2

# ベルギー IMEC (Interuniversity Microelectronics Center)

ベルギーに本拠を置くIMECでは、2004年からTSV技術への基礎技術の取り組みを開始し、2006年からIIAP(IMEC Industrial Affiliation Program)という3次元集積の個別プロラムを用意して、産業化活動を活発化させている。そのゴールは、3次元実装領域のテクノロジと設計問題の探求である。このプロジェクトには以下の特徴がある<sup>25、26)</sup>。

#### (1)参加メンバーの多様性

協業のパートナーは世界中から 集まる、IDM (integrated device manufacturer;設計から製造、販売ま で行う半導体メーカー)、パッケー ジング会社、製造(全部/一部)委託 の半導体メーカー、EDAツール開 発会社、半導体製装置メーカー、 材料メーカーである。

#### (2) 革新的な解決法へのアプローチ

研究範囲は、パッケージレベルから LSI チップ内にまで入り込んだ、異なる配線階層での3次元配線となっており、コストを意識した実用化へ向けての技術探求とと

図表 9 代表的な公的研究拠点

| 組織名称                                                       | 所在地        |

|------------------------------------------------------------|------------|

| SEMATECH(Semiconductor Manufacturing Technology Institute) | 米国         |

| ジョージアエ科大学                                                  | 米国         |

| マサチューセッツ工科大学                                               | 米国         |

| レンセラー工科大学                                                  | 米国         |

| RTIインターナショナル                                               | 世界各地 (米国発) |

| アーカンソー大学                                                   | 米国         |

| MITリンカーンラボラトり                                              | 米国         |

| IMEC(Interuniversity Microelectronics Center)              | ベルギー       |

| CEA-Leti(フランス原子力庁電子情報技術研究所)                                | フランス       |

| フラウンホーファー 信頼性・マイクロインテグレーション研究所                             | ドイツ        |

| IME (Institute of Microelectronics)                        | シンガポール     |

| ITRI(Industrial Technology Research Institute)             | 台湾         |

| ASET(超先端電子技術開発機構)                                          | 日本         |

| 東北大学                                                       | 日本         |

参考文献5を基に科学技術動向研究センターにて加筆して作成

もに、革新的な解決法の提案を求めている。特に、システムレベルで3次元配線を利用可能にする重要な設計問題における設計領域の探求と設計法の提案を目標としている。TSV技術のロードマップも示されており、将来的には、TSV径を $0.1~\mu$ mにまで微細化した、LSIのトランジスタレベルの精度での回路間接続を目指している。これは、2-2項で述べた「SoC の発想転換 | の具体的な動きである。

#### (3) その他の特徴

IMECにはEDAツール開発会社が協力している点で、SEMATECHの取り組みとは異なる。また、IMECは大学である立場から、このプログラムとは別に独自の先端研究を行っており、半導体製造技術の研究ではSEMATECH同様、世界トップレベルの知見の蓄積がある。IMECで開発された世界最先端の半導体製造装置を利用できることが、このプログラムへの参加を促す、外部へのアピールになっている。

### 4-3

### 欧・米・韓による EMC-3D (Semiconductor 3-D Equipment and Materials Consortium)

EMC-3D という、欧・米・韓にまたがるプロジェクトは、2007年にフランスの CEA-Leti が参画を表明し、活動を開始している。EMC-3D の活動の目的は、3 次元チップ積層と MEMS 集積化のための、コストを考慮した TSV 技術の開発である。このプロジェクトには以下

の特徴がある 27)。

### (1) グローバルな参加メンバー

EMC-3Dは国際コンソーシアムの形態をとっており、欧・米・韓にまたがる、材料メーカー、半導体製造装置メーカーのほかに、大学や企業の研究開発部門がパートナーとして参加している。

#### (2)業務分担によるアプローチ

各参加メンバーはその専門分野別の研究開発テーマを持っており、TSVの形成技術、ウェハーの研磨技術、LSI積層の技術、実装技術などの研究目標を分担している。全体的には、低コストのTSV技術の実用化を目指し、完成度の高い試作を繰り返している。

#### (3) その他の特徴

半導体製造会社自体は参加メン バーになっておらず、メーカー組 織内の研究所が参加している点に 特徴がある。また、公的研究機関 としては、ドイツのフラウンフォー ファー研究所、フランスの CEA-Letiなど、基礎技術を研究してい る組織が関与している。これらの 取り組みは、SEMATECH同様、 産業上の非競争分野を狙っている と考えられる。EMC-3Dは、日本 の ASET プロジェクトに対抗して 組織されたプロジェクトであると 言われている。このため、日本を 除いた主要な組織が参加している コンソーシアム形式のプロジェク トになっている。

### 4-4

### 日本 技術研究組合 超先端 電子技術開発機構(ASET)

TSV 技術の実用化研究で日本の ASET は、世界に先駆けて、1999 年にコンソーシアム形式のプロジェクトとして立ち上げ、活動を 開始した。現在は、「立体構造新機能集積回路(ドリームチップ)技術開発/多機能高密度三次元集積化技術」をテーマにして、TSV 技術の 実用化を見据えて研究開発を行っている。

### (1) 実用化を見据えた参加メンバー

参加メンバーは、電子機器メーカー、半導体メーカー、材料メーカー、半導体装置メーカー、パッケージング会社など、TSV技術の実用化を見据えた産業界に加えて、複数の大学、(独)産業技術総合研究所(AIST)から成る<sup>12)</sup>。

### (2) 実用化を検証するプローチ

資金は、(独)新エネルギー・産業技術開発機構(NEDO)からの委託事業から得て、研究が行われている。回路および電磁界シミュレーション、インタポーザを利用したSIおよびPI技術、テスト技術、熱設計技術、研磨技術、TSV技術を導入したLSI部品の試作など、TSV技術の実用化に近い研究開発が行われている12.28)。

### (3) その他の特徴

参加メンバーである半導体装置メーカーは、TSVの穴開けなどに関わる製造装置のメーカーだけでなく、テスト技術などを得意とするメーカーが参加している点で、他のプロジェクトと異なる。また、TSV形成にかかる各工程の要素技術のほとんどは、すでに完了したものと位置付けており、現在は、製品化を意識した周辺技術(3-2項)の開発が主な研究対象になっている。

## 5 おわりに

TSV 技術は、従来の微細化の追求に代わり得る高集積化のための 実装技術として注目されていると ともに、複数の異種 LSI チップや MEMS を混載して多機能 LSI を実 現できる点でも、その適用に大き な期待が寄せられている。

TSV 技術に関する各国のプロジェクトを概観すると、TSV 技術の基本技術とその応用の研究開発に余念のない米国の拠点、EDAツールの新規開発と技術適用の将来展望を持って TSV 技術の実用化にも力を入れている欧州の拠点、基礎技術を有しながら TSV 技術適用の実用試作に注力している欧・

米・韓連合のコンソーシアム、周 辺技術などを抑えて実用化に取り 組む日本のコンソーシアム、とい う違いが窺える。中でも日本の研 究体制は最も「出口」に近いところ で行われているようである。

TSV 技術の導入には、小型・高密度化のほか、高速化、省エネ化、多機能・高機能化などメリットは多いが、解決すべき技術課題も多く抱えている。課題は、設計技術、TSV 形成の製造技術、そして実用化に至る周辺技術まで範囲は広く、その解決に向けた研究拠点の活動は世界中に広がっている。これらは総じてグローバルな連携を志向

した動きであり、最先端の LSI 開発技術の進め方として、グローバルな連携というキーワードは注目していく必要があろう。

### 謝辞

このレポートを作成するにあたり、東北大学 小柳光正教授、東北大学 小林広明教授、研究組合超先端電子技術開発機構(ASET)嘉田守宏部長、IMEC (Interuniversity Microelectronics Center) 日本代表部 石谷明彦博士に多くの情報と助言を頂きました。深くお礼申し上げます。

### 参考文献

- 1) 黒田研究室ホームページ: http://www.kuroda.elec.keio.ac.jp/publication/paper\_and\_lecture/2009.html

- 2) 岩田穆 ほか 「(招待講演)無線/光配線による三次元集積の課題と展望」 信学技報 vol. 108, nNo.140 ICD2008-53, pp89-94, 2008 年 7 月

- 3) 広瀬全孝 ほか 「三次元光結合共有メモリ集積装置」 特開昭 61-003450 1986 年 1 月 9 日 (公開)

- 4) 山田隆章 「積層チップ」 特開 2010-016238 2010年1月21日 (公開)

- 5) 盆小原学 ほか「SiP 技術と三次元実装技術の動向と将来」 招待論文 電子情報通信学会論文誌 C Vol.J87-C No.11 pp.791-801 2004 年 11 月

- 6) J.U.Knickerbocker et al. \[ \text{Development of next-generation system on package (SOP) technology based on silicon carriers with fine-pitch chip interconnection \] IBM J. RES. & DEV. Vol.49 No.4-5 July/September 2005

- 7) P.Ramm 「EUROPEAN ACTIVITIES IN 3D SYSTEM INTEGRATION THE e CUBES PROJECT」 12<sup>th</sup> Annual Pan Pacific Microelectronics Symposium Maui, Hawaii, February 1,2007

- 8) (株) 東芝プレス発表(2007 年 10 月 1 日): http://www.toshiba.co.jp/about/press/2007\_10/pr\_j0102.htm

- 9) エルピーダメモリ(株) プレス発表 (2009 年 8 月 27 日): http://www.elpida.com/ja/news/2009/08-27.html

- 10) 傳田精一 「3 次元チップ積層のためのシリコン貫通電極 (TSV)の開発動向」 表面技術 Vol.58、No.12 2007 年

- 11) 小林 「Greeting and opening Remarks by Cyberscience Center」 11th Teraflop Workshop Oct. 19-20, 2009)

- 12) 嘉田守宏「3 元集積技術の開発動向と低コスト化に向けた展望」 TSV テクノロジ・コンファレンス 2009・セミナー 日経マイクロデバイス社主催 2009 年 4 月 16 日

- 13) http://ja.wikipedia.org/wiki/%E6%B7%B1%E5%A0%80%E3%82%8ARIE

- 14) http://ja.wikipedia.org/wiki/%E5%8F%8D%E5%BF%9C%E6%80%A7%E3%82%A4%E3%82%AA%E3%83%B3%E3%82%A8%E3%83%B3%E3%83%B3%E3%82%B0

- 15) http://www.necel.com/fab/ja/line/line1.html

- 16) 加藤理「貫通電極を用いたチップ積層技術の開発」OKI テクニカルレビュー第 211 号 Vol.74No.3 2007 年 10 月

- 17) S. Arkalgud「Challenges in 3D TSV Technology」SEMICON West 2009 2009 年 7 月 15 日

#### 科学技術動向 2010年4月号

- 18) 一般財団法人 VCCI 協会ホームページ: http://www.vcci.jp/general/objective.html

- 19) NIKKEI MICRODEVICES 2009 4 月号 No.286 pp18-pp21 2009 年 4 月 1 日

- 20) NIKKEI MICRODEVICES 2009 12 月号 No.294 pp95-pp98 2009 年 12 月 1 日

- 21) SEMATECH ホームページ: http://www.sematech.org/research/3D/index.htm

- 22) SEMATECH ニュースリリース: http://www.sematech.org/corporate/news/releases/20070321.htm

- 23) (株)東京エレクトロン プレス発表: http://www.tel.co.jp/news/2009/1203\_001.htm

- 24) SEMATECH プレス発表: http://www.sematech.org/corporate/news/releases/20081029.htm

- 25) IMEC ホームページ (IIAP): http://www2.imec.be/content/user/File/Leaflets/cmos-iiap-3D-2009\_EN.pdf

- 26) IMEC ホームページ: http://www.imec.be/ScientificReport/SR2008/HTML/1224952.html

- 27) EMC-3D ホームページ: http://www.emc3d.org/index.html

- 28) ASET ホームページ: http://www.aset.or.jp/kenkyu/project.html

### 執筆者プロフィール

吉永 孝司

情報通信ユニット 科学技術動向研究センター 特別研究員 http://www.nistep.go.jp/index-j.html

ICT企業で EMC (電磁環境両立性)規格を担当し、同・国際標準規格の制定に寄与。 その後同社で電磁ノイズに対する電子機器の耐性向上の研究に従事し、2008 年より 現職。専門は電磁波測定と耐電磁ノイズ設計技術。

野村 稔

科学技術動向研究センター 客員研究官 http://www.nistep.go.jp/index-j.html

企業にてコンピュータ設計用 CAD の研究開発、ハイ・バーフォーマンス・コンピューティング領域、ユビキタス領域のビジネス開発に従事後、現職。スーバーコンピュータ、LSI 設計技術等、情報通信分野での科学技術動向に興味を持つ。