科学技術動向 概 要

本文は p.23 へ

## LSI の配線設計の課題と 設計自動化ツール開発の重要性

集積度向上、微細化の進展によって、LSI(大規模集積回路)の性能向上には著しいものがある。その一方で、「配線問題」がクローズアップされて来た。LSIの設計・製造において、配線が主要な制約要因となりつつあるという問題である。配線とは、回路素子、ゲート、マクロなどの回路部品間を相互接続するものであり、「配線問題」とは、この配線を、設計、製造を通して如何に最適に実現するかという問題である。

従来、LSIの開発工程は設計工程と製造工程に大別され、更に設計工程は論理設計と配線設計に分かれていた。そして、それらの間のインターフェースも固定していたため各工程内で作業を完結することができた。ところが近年、微細化の進展により設計に大きな変化が起こっている。配線の遅延時間の影響が無視できなくなり、配線設計後に論理設計へ手戻りが発生するなど、従来の固定したインターフェースが崩れ、論理設計と配線設計を一体のものとして考える必要が出てきた。さらに、微細化の進展により製造歩留まり低下の問題を解決するために、設計工程の中で製造性を考慮した設計(設計と製造の融合)が必要となってきた。これらの変化は共に「配線問題」に起因している。

「配線問題」の解決には、製造技術と設計技術が共に優位性を持つことが必要である。製造技術を支える材料・構造や配線技術は、日本の大学および企業でも高度な研究が進められており、世界的に認知度も高く優位性は高いと言える。一方の設計技術は、設計自動化(EDA: Electronic Design Automation)ツールに依存しており、EDAツールでは圧倒的に米国が優位にある。ここでは、将来の配線問題に備えた設計技術の強化を目指し、我が国の優れた製造技術のノウハウを取り込んだ設計技術の実現に向けて、以下の施策の推進を提言したい。

- (1)核となる EDA ツールの開発:「すりあわせ」の技術で強さを発揮できる領域に絞った開発と、この開発を通した設計ノウハウと技術力の蓄積、継承そして保護

- ①「製造技術」を活かす先行開発:製造歩留まりの定量的把握に基づいた設計ルールの設定、新設計手法の構築、革新的 EDA ツールのタイムリーな先行開発

- ②異研究領域のコラボレーション:設計と製造、シリコンとナノテクノロジーの領域 のコラボレーションの推進

- ③企業主体のコンソーシアムへの大学研究者の積極的参加

- (2)積極的な知財活動の推進:ノウハウの無意識な流出を防ぎ、その価値を意識した知財の保護

- (3)ターゲットを決めた推進:波及効果を生むターゲットの設定とロードマップの作成

# LSIの配線設計の課題と 設計自動化ツール開発の重要性

野村 情報・通信ユニット

# はじめに・

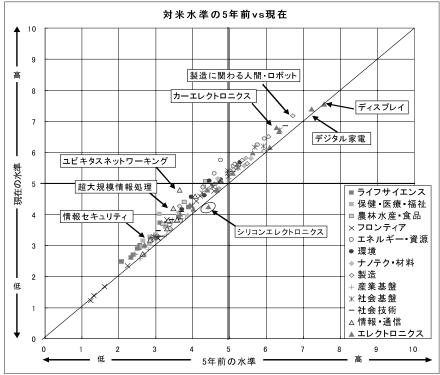

科学技術政策研究所が行なっ た「科学技術の中長期発展に係る 俯瞰的予測調査」での「デルファ イ調査報告書」1)に、我が国の研 究開発水準の調査結果がある。図 表1は、このなかの現在と5年前 の対米国の研究開発水準を示して いる。5年前に比べほとんどの領 域で水準が上昇していると判断さ れている。しかし、シリコンエレ クトロニクスの領域は、唯一、水 準が低下していると指摘されてい る。デルファイ調査では、各領域 がもたらす「知的資産の増大」「経 済的効果 | 「社会的効果 | の程度 も評価しており、シリコンエレク トロニクスは、それらの全軸で効 果が高く重要な領域として位置づ けられている。それにも拘らず、 その研究水準が落ちてきていると の結果である。

現在、シリコンエレクトロニク ス領域では、「システムの複雑化 に対応する設計の高度化、デバイ ス・配線の微細化の物理限界への 接近」などで生じる様々な課題に 直面している。ここでは、そのな

かでも、高速 LSI 実現に最も直接 的に影響する「配線問題」に焦点 を当て議論の掘り下げを行う。以 下では、シリコン CMOS ロジック LSIを対象とし、「配線問題」とは

図表 1

何かを示し、配線問題に関わる製 造技術と設計技術の研究開発、そ れらの現状および課題を抽出し、 今後の対策と提言を行いたい。

対米水準の5年前vs現在 10

現在と5年前の対米国研究開発水準

「科学技術の中長期発展に係る俯瞰的予測調査」の結果より

# 配線問題とは・

LSIでは、トランジスタや抵抗 などの回路素子の組み合わせによ りANDやNANDなどの基本的 な論理ゲートが構成され、ゲート

を組み合わせて更に複雑な論理機 能を持つマクロが形成される。こ れら回路素子、ゲート、マクロ(以 下ではこれらを回路部品と呼ぶ)

間を相互接続するものが配線であ る。広義には回路部品への電源や グランド供給線も配線に含まれる が、以降では LSI 性能に焦点を絞 るため、主に信号に関する配線について述べる。配線は、半導体の微細化に伴い LSI の性能や製造性を決定付ける大きな要因として浮

上してきており、「配線問題」とは、 設計および製造を通して、この配 線を如何に最適に実現するかとい う問題である。

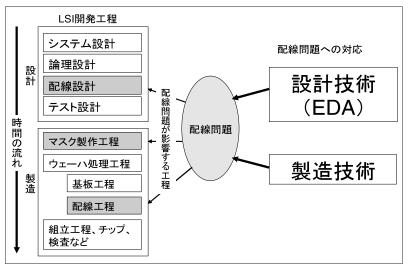

図表 2 LSI 開発工程と「配線問題」

科学技術動向研究センターで作成

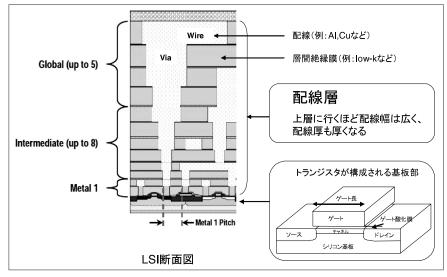

### 図表3 LSIの多層配線構造

ITRS 2003 資料<sup>2)</sup> を基に科学技術動向研究センターで編集

#### ■用語説明■

### ①配線設計

狭義には回路部品間の配線パターンの設計をさすが、ここでは、回路部品の配置、その間の配線、信号のタイミング検証、電気的検証、デザインルールチェック、マスクデータ生成など物理的な設計に関係する設計全般と広義に捉える。物理設計またはレイアウト設計とも呼ばれる。

### ②リソグラフィ

回路パターンなどを「現像」する装置、またその過程をいう。

#### ③設計技術

LSI を設計する技術であり、アーキテクチャ、回路など設計そのものと、それを支援する設計手法からなっている。ここでは、EDA ツールを基盤とした設計手法に支援される LSI 設計の技術を「設計技術」と呼び、以降の議論の対象とする。LSI の高集積化、高速化に伴い「設計技術」は、EDA ツールに大きく依存し、「設計技術」の進展は EDA ツールの進展と密接に関係し分離できないものとなっている。

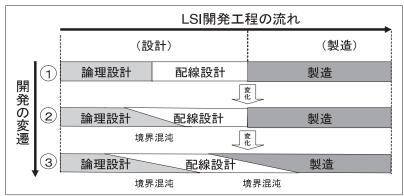

図表 2 に、LSI 開発工程とその中での「配線問題」の位置づけを示す。LSI 開発工程は大きく設計と製造に分けられる。「配線問題」は、設計においては配線設計<sup>①</sup>に、製造においては、マスク製作工程と配線工程に影響する。

ここで、配線設計とは、回路部 品の配置とその間の配線を行い、 製造で使用するマスクデータを 作成する作業である。マスク製作 工程とは、マスクデータを起点と してリソグラフィ<sup>②</sup>を考慮したマ スクを製作する作業である。そし て、配線工程とは、ウェーハ上で 物理的な配線を実現する工程であ る。「配線問題」への対応として は、設計自動化 (EDA) ツールを 基盤とした設計手法(設計方法論 とも呼ぶ) に支援される「設計技 術」③、材料・構造、配線技術に より配線を物理的に実現する「製 造技術」のバランスある進展が求 められる。

# 配線構造

図表3では、LSIの多層配線構造を例示している。LSIは、下からシリコン基板、その上にトランジスタや抵抗などが形成される基板部、そして回路部品間を接続する配線層からなる。

配線層は、水平と垂直の層が 交互に設けられており、配線はこれらの層上で立体交差状に実現を れている。この水平、垂直層を 互に積層した三次元構造を多層配 線構造では、トランジスタや抵抗 間をつなぐ短い配線は Metall 層、 クロック信号のように LSI 全体に 配られる Global 信号配線は Global 層、電源やグランド供給の配線は 最上層、それ以外は Intermediate 層を用いるなど、各配線層の使い 分けが行われている。微細化の進 展により最近の LSI では配線本数

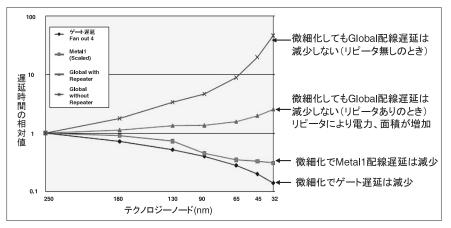

### 図表4 微細化にともなう配線遅延

ITRS 2003 資料<sup>2)</sup> を基に科学技術動向研究センターで編集

は数千万本にも達しており、配線 層数も次第に多くなり、製造工程 における配線工程の割合が大きく なってきている。

### 信号伝搬遅延時間

配線上を信号が通ると伝播遅延 時間が生じる。配線は抵抗と容量 を持ち、これらを配線抵抗と配線 容量という(隣接配線との間には 寄生容量も生じるが、この配線容 量に含めて考える)。伝播遅延時 間は、容量と抵抗の積に比例する ため、配線抵抗と配線容量が大き な長い配線は伝搬遅延時間を大き くしてしまう。理想的には微細化 により配線の容量も減るはずであ るが、配線間の距離が小さくなる ため結合容量が大きくなり、また 微細化すると配線の幅が狭くなる ため、結果的には配線抵抗が増し てしまう。図表4は微細化、高性 能化での配線遅延の影響を例示し ている。

図表4は、配線材料としてCu、層間の絶縁膜として低誘電率 (low-k) 材料を用いた場合のゲート遅延と配線遅延の相対的な割合を示している。ゲート遅延と Metall の配線遅延は微細化に伴って減少するが、Global 配線の遅延時間は増加する。これを解決するため、一般にはリピータと呼ばれ

るバッファ回路を挿入することでドライブ能力を上げて遅延時間を改善する方法が採られるが、代わりに消費電力と面積が増加してしまう。このようにテクノロジーノード(ノード:最小配線ピッチの1/2)が250nm以降の世代からは、ゲート遅延より配線遅延がLSIの動作速度を律速する主要因として顕在化してきている。高速化のためには配線遅延の最小化が必須である3)。

この配線遅延の影響で最も深刻 なのは、動作周波数の高速化にお けるクロック分配とクロックスキ ユーに関する問題である。現在の LSI 設計においては、同期式回路 が主流を占めている。同期回路に おいては、回路中の数万~数十万 ビットといったフリップフロッ プ④全てにクロック信号が同時に 到達する様に供給される必要があ る (クロック分配)。しかし、現 実には、配線遅延時間の差がクロ ックスキューと呼ばれる到達時間 のばらつきを生む。クロックスキ ユーは、クロック周期の短縮の妨 げとなるばかりでなく、その大き さによっては回路の誤動作の原因 になる。クロック周期の短縮に伴

い、クロックスキューの性能に与 える影響が相対的に大きくなって いる。

### 配線に起因する その他の問題<sup>4)</sup>

### (1)クロストークノイズの発生

配線間の距離が短くなるにつれ、隣接する配線間で生じる容量が増加し、信号の漏れ(クロストーク)が発生する。隣接配線の電位変化により、配線間の容量が変わるため遅延時間が変動する問題もあり、これもクロストークにより、シグナルインテグリティと呼ばれる「信号波形の品質」が悪化し、回路の誤動作を引き起こす可能性があるため、適切な対処が必要になる。

### (2)配線による消費電力増大

電力消費の主役は、かつてはゲ ートであったが、今日では LSI 上 の配線が膨大になり、配線容量を 充放電するための電流が CMOS デバイスの抵抗でジュール熱(導 体に電流を流すとき導体の抵抗の ために発生する熱)を発生させ、 これによる電力消費が支配的にな っている。特に、クロック信号は LSI全体に分配されるため配線本 数が多く、かつ長い配線が多い。 そしてクロックごとにスイッチン グするため電力消費はますます膨 大になる。このクロック配線にお ける消費電力削減は大きな課題で ある。

### ■用語説明■

### ④フリップフロップ (Flip-Flop)

「high」と「low」の2つの安定状態を持つ電子回路で記憶回路の一種。次のクロックが加えられるまでは以前の状態を保持する働きをする。

### (3)エレクトロマイグレーション

エレクトロマイグレーションと は、高密度電流を流したときに配 線中の金属イオンが電子からの衝 突を繰り返し受け、金属の原子配 列が乱れて断線してしまう現象で ある。微細化により配線が縮小し、 一方で動作速度を上げるために駆 動電流が増大している。すなわち 電流密度は増大傾向にあり、エレ クトロマイグレーションはますま す起こりやすくなる。

# 3

### 配線の製造技術に関する研究開発・・・

配線工程の製造技術は、プロセス、製造装置、製造ラインにまたがる技術であるが、ここでは性能に関わるプロセスにおける配線材料・構造と配線技術の研究開発について述べる。

3 -

### 材料・構造の研究開発

配線工程の配線層形成、絶縁層 形成、層間接続構造形成などのプロセスの各分野においては、材料・ 構造面の各種の研究開発が行われている。具体的には、配線抵抗が小さい材質(Cu)への変更や、配線容量を低く抑えられる低誘電率(low-k)材料の開発、ビア(配線層間をつなぐ金属配線)形成方法の研究開発などが主体である³)。

3 - 2

### 今後の配線技術

配線技術の研究開発では、配線 長短縮方法や、高速伝送のために 電磁波や光を活用した技術が提案 されている。

### (1)オンチップの伝送線路配線

伝送線路は、電磁波の速度で信 号伝送を行うものである。長距離 伝送において低消費電力で高速な 信号伝送が実現可能となる。差動 伝送線路は2本の信号線の電圧の 差で信号を伝えるため、線路外からのノイズをキャンセルすること ができ、小振幅での信号伝送が可能になる。オンチップ(チップ上 の)伝送線路配線では高速信号伝 搬が実現できるが、一般の配線構 造と比較して配線面積を必要とするという欠点も併せ持つ。クロック配線や長距離信号配線に選択的に採用することで高速化が期待できる5、6)。

### (2)三次元積層

三次元積層とは、複数のLSIを積み重ねて相互間を接続する方式である。有線と無線による接続方式の研究が行われている。三次元積層でのLSI間接続においては、LSI周辺に配線を引出して接続する方式に比べ、信号伝送距離が垂直分の距離だけで済むため、伝搬遅延時間を短くすることができる。

有線での三次元積層では、LSIに貫通する埋め込み配線を形成し、LSI同士を張り合わせていく方式で積層する。LSIを複数個積み重ね、LSIを貫通する埋め込み配線を用いた垂直配線によってLSI間を電気的に接続する。この技術により、世界初の三次元積層型の人工網膜チップおよび視覚野チップの試作を行うなどといった先端研究も進められている7)。

無線による接続方式は、インダクタ結合や電磁波伝搬などの無線手段を用いて通信する方式である。インダクタ結合では、多数のインダクタ対をLSI上の任意の位置に形成し、隣接LSI間を磁力線で無線通信する8~10。また、電磁波伝搬では、LSIを透過したで高高波を伝搬させることができ、各LSIに形成したマイクロアンテナで送受信する。複数のLSIを更ってデータを転送であい、システム全体のクロック供給

やデータの同時伝送に用いること ができる<sup>8)</sup>。

三次元積層は、LSI平面上に異なる LSI 間の接続を多数設置できるため、LSI 間の並列データ転送が可能になる長所も持ち、高性能処理に必要な CPU とメモリ間の高速通信の可能性を持つ。現在のEDA ツールは二次元レベルの設計機能にとどまっており、三次元で必要となる回路部品の配置・配線や解析に向けては新たなツールが必要となる。

### (3)オンチップ光配線

シリコン光導波路、フォトニッ ク結晶、ポリマー光導波路など、 オンチップの光配線に適した幾つ かの有望な要素技術がすでに現れ てきている。シリコンを使っても 超高速となるナノフォトダイオー ド(受光素子)などによる光-電 気変換素子も研究開発が進んでい る11)。この分野では、従来は化合 物半導体での開発が中心であった が、最近は汎用性が高くコストも 有利なシリコンプロセスでの研究 が進展してきた。また、シリコン を用いて光を増幅できる連続発振 レーザの研究も発表されており、 将来的にはコンピュータの内部を 光速でやり取りできる光デバイ スを安価で実現できる可能性もあ る<sup>12)</sup>。

オンチップ光配線は、配線同士がクロスしても干渉がないこと、配線が近接してもクロストークがないことなどの利点を持ち、クロック分配などに利用することで高速化が期待できる。

### (4)配線に関する研究開発体制の動き

米国では、従来から共同研究 開発会社である Microelectronics Advanced Research Corporation (MARCO) が米国の大学での半 導体研究に資金を出し、Focus Center Research Program (FCRP) という研究開発計画を進めてい る。この中に Interconnect Focus Center (IFC) があり、電気や光 配線などの先端研究が行われてい る また、企業コンソーシア ムである SEMATECH でも三次 元配線に関する研究を計画している <sup>14)</sup>。

我が国では、独新エネルギー・産業技術総合開発機構(以下、NEDOと呼ぶ)が、2005年10月13日に「次世代半導体材料・プロセス基盤プロジェクト(MIRAI)において計画している産学官連携研究に関する先導調査」と題する公募 <sup>15,16)</sup> を行った。この研究開発項目として、「新探究配線技術

開発」があり、技術世代 45nm ノードを超えた集積回路に適した配線基盤技術開発として、①極限低抵抗配線技術と②新コンセプトグローバル配線技術の開発が取り上げられている。例として、カーボンナノチューブ(CNT)等の新材料を使った極限低抵抗配線技術の開発や、光配線技術や RF (高周波)配線技術等の開発などが挙げられている。

### 配線の設計技術に関する研究開発

「設計技術」は、アーキテクチ ャ、回路など設計そのものとそれ を支援する設計手法からなってい るが、以下では、最も注目すべき EDA ツールを基盤とした設計手 法に支援される LSI 設計技術に焦 点をあて、その概要を述べる。こ こで言う設計手法とは、如何に最 適に LSI を設計するかの方法論で あり、EDA ツールを駆使した設 計フロー、ライブラリ、設計機器 などの構成要素からなる設計環境 として具現化される。設計は、シ ステム設計、論理設計、配線設計、 テスト設計、そして回路部品を設 計する回路設計等からなるが、こ こでは、そのうちで配線問題に大 きく関係する配線設計について述 べる。

配線設計の役割の第一は、指定された大きさのLSI内に回路部品を配置し、回路部品間に要求された配線を誤りなく収容することである。それと共に、所望の性能を得るためのタイミング設計、各種検証などの処理が必要になっている。以下、主だった内容を示す。

#### (1)設計ルール

使用可能な材料・構造、配線技術をベースにしてLSIを設計するためには、設計基準(デザインルール)が必要になる。設計基準と

は、回路素子の各部分の平面的な 寸法や隣接する部分との間隔、さ らに回路素子間の立体的な相互の 位置関係などを決めた基本的な規 則である。設計基準は、微細化さ れた回路素子や配線を LSI 上に実 現し、安定的に量産するために必 須となる基準である。配線設計で は、この設計基準以外に、配線の 抵抗、容量、隣接または上下層間 の配線容量、クロストーク量など 様々な電気的な制約を規定するこ とで設計が正しく進められるため のガイドが設けられている。この ようなガイドを含めて、これらを 設計ルールと呼んでいる。設計ル ールは、製造技術を生かして配線 設計を行うためのインターフェー スであり、その遵守により正常な 設計が可能になる。

### (2)タイミング問題への対応

タイミングが合わなければ、論理回路は正しくてもLSIは正常に動作しない。タイミングの設計は近年のLSI開発における最大の難問である。その設計の難しさは遅延制約の遵守にある。遅延制約とは、全てのフリップフロップへの同時クロック分配、信号伝搬における許容時間制限などである。許容時間制限とは、フリップフロップの出力データが次のフリップフ

ロップまたは外部端子に伝播する 時間に、下限値および上限値があ り、これを全ての信号線に対して 満たすという制限のことである。

タイミング問題への対応としては、クロック信号の分配方式、クロックに号の分配方式、クロックスキューの最大値を最小化する自動配置配線、タイミング制約違反箇所へのバッファ回路挿入や配線幅調整、そして以下の(3)で示すタイミング検証ツールなどがある。

参考文献17にはマイクロプロセッサ用のタイミングを考慮した設計手法が示されているが、設計期間の大部分をタイミング改善に費やしていることがわかる。タイミング制約を満たす設計の複雑さを表す事例である。

### (3)設計の検証

設計ルールを完全に満たすような自動設計はまだ実現されてない。現実には、自動ツールによる配置・配線と人手による設計が混在しているため、設計ルールが遵守されているかを検証する必要が生じている。検証の代表的なものに、前記した設計基準が満たされているかを検証するDRCがあり、これまで設計と製造の間のコミをとしてきた。しかし、製造での果たしてきた。しかし、製造での

歩留まり問題を解決するにはこれ では十分でなくなってきている。

タイミング問題に対しては、全 論理パスにわたって遅延制約を検 証する静的タイミング検証、LSI の製造ばらつきを考慮した統ツール化が行われている。クロストークノイズに対しては、LSI内の各信号線から受けるトークノイズを遅延時間に換算しがある。また、その他の検証するツールなどがある。また、その他の検証である。また、その他の検証であれて、電磁界解析、熱解析などがあ り、これらも重要性が増してきている。

検証ツールは、事実上、計算 機処理の自動ツールで実現できない機能の補完をしてきたことになる。検証結果による不具合箇所の 修正は、人手を介して行われてき たが、これが膨大な時間と品質上 の問題を招いているため、自動ツ ールへの機能組込みが進められつ つある。

### (4)配線設計における EDA ツールの研究動向

1980年代に配線設計用 EDA ツール開発は活況を呈したが、その

後、配置・配線処理の機能向上が一段落し、研究対象は上流のシステム設計や論理設計分野に向かった。その結果、配線設計の研究は、1990年代は下火になった。しかし、1990年代終わりからは、微細化に伴う配線設計の複雑化により、配線設計用EDAツール開発が再び脚光を浴びるようになった。2005年6月の第42回設計自動化会議(DAC:Design Automation Conference)では、配線設計関係(Pysical/Circuit design,Timing & DFM)での論文数が65件と全体の約35%を占めている。

# 5

### 設計技術の状況変化と課題・・・・・・・・・・

2章で、「配線問題」は、「製造技術」と「設計技術」のバランスのうえで改善していくと述べた。 我が国のこれらの技術の優位性はどうであろうか。

1軸目の「製造技術」である が、かつて我が国の「製造技術」 は世界をリードしていた。しか し、DRAM 競争で韓国の後塵を 拝したこと、パーソナルコンピュ ータ分野のマイクロプロセッサで 標準化が出遅れたこと、台湾にお けるファンドリ・ビジネスの進展 の逆風にさらされたことなどで、 現在は活況さを欠いている。ただ し、設計と製造の垂直統合で培っ た「製造技術」は、世界的なレベ ルとして、依然として高いものを 堅持している状態と言える。配線 技術の分野に限っても、大学およ び企業で高度な研究が進められて おり、世界的な認知度も高い。

一方、2軸目の「設計技術」はと言うと、EDAツールにノウハウが集約されており、ここでは米国の優位さが圧倒的である。「配線問題」の解決に向けては、2軸のバランスある発展が必要になるため、EDAツール依存の「設計

技術」の弱体さが問題となる。今日の先端技術の開発には、「すりあわせ」の技術開発が必要になってきており、「設計技術」の強化は必須の課題である。以下では「設計技術」面における状況の変化と課題を述べる。

# 設計技術の状況変化

図表5は、LSI 開発工程の中での配線設計の位置づけと、微細化の進展による開発の変遷を示している。LSI の開発工程は設計と

製造に大別されることを前述したが、はSIの物理特性に依存する分とを有するの物理特性に依有する分とをできることができることができることができることができることが変化できることが変化が変化が変化が変化が変化が変化が変化が変化が変化を対したというのといる。との後子を図表 5 に示す。

(注) ここでは説明上、システム、テスト設計をはずした。

科学技術動向研究センターで作成

# (1)論理設計と配線設計の分離の時代(図表5の(1))

以前、設計部門での工程は、論理の正当性を確認した後、配線設計を行っていた。両工程は、設計変更が生じると繰り返されるため完全な分離はできないが、基本的には論理設計と配線設計とは分離していたと言える。

# (2)論理設計と配線設計の融合 (不分離)の時代(図表5の②)

微細化の進展により配線遅延が ゲート遅延に比べて支配的になる と、単純に論理設計した結果を基 に配線するだけでは全体の遅延時 間を満たした設計ができなくなっ た。そのため、配線した結果を基 に論理設計内容を変更する方法が 採られるようになった。配線結果 から遅延時間を求め、信号が伝搬 する論理パスの中からクリティカ ルとなるパスを求め、このパス上 に存在するゲートのドライブ能力 を変更するなどの補正により論理 と配線との整合をとる設計となっ た。図表5では、この時代を論理 設計と配線設計の融合(不分離) として表した。

# (3)設計と製造の融合(不分離)の時代(図表5の③)

微細化が更に進むと、製造上で の露光装置の限界から、新たな 問題が発生してきた。配線幅が 露光波長より細くなってきたた

### ■用語説明■

### 5位相シフトマスク

位相シフタを通過して位相の変わった光とシフタを通過していない位相の変わっていない光との干渉を利用して 解像度を向上させる方法。

#### ⑥ OPC マスク(光近接補正)

パターン形状の向上のために補助パターンなどを付加する方法。

5 - 2

### 設計と製造との境界の変化

設計と製造の融合(不分離)の 状態を説明する端的な例として、 ウェーハの露光時のパターン解像 度を高めるために、設計の段階で フォトマスクにあらかじめ細工⑤ しておく「位相シフトマスク⑥」18)などの対策の はいる。このように、製造のが 留まりを回数ないう、設計を やビアはるという、設計を やビアはるという、設計を を受けるという。 強くなっている。

(株)半導体理工学研究センターの下東氏は、次の様に述べ、この設計と製造との境界が変化している問題を重要視している。「ナノメータ CMOS 時代を迎え、突破しなければならない壁/ボトルネックの1つとして DFM (Design For Manufacturability) がある。DFM とは製品の製造性を最大にするような設計全般の活動と定義される。ナノメータ時代の DFM はその規模と複雑性で特筆されるべきものである。微細化によってもたらされた副次効果が脅威へと変化し微細化そのものを律速する

ことになった。設計と製造が協調してシステマチックに問題対応できる新しいワークフローが不可欠である。」<sup>19)</sup>

5 - 3

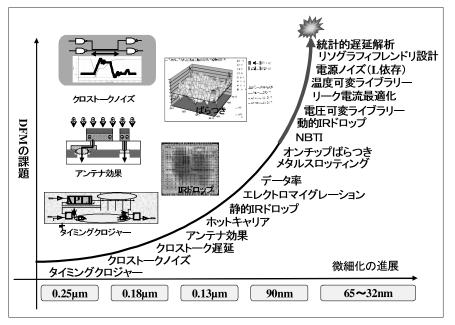

### 設計課題の増加

図表6では微細化に伴う設計課題の増加を示している。新たな課題が次々に顕在化し、顕在化した課題が微細化の進展でさらに複雑な課題となり、課題の複雑さが指数関数的に増加していく。

ある CPU チップの実績では、トランジスタ数が 6,000 万であるのに対し、LSI 内の総配線長は数100 メートルを越え、配線間を結ぶビア数に至っては 10 億に近いものとなっている。配線数が多い LSI の歩留まりが極端に悪いという事例も出てきており、歩留まりを決めているのはトランジスタではなく配線であるとも考えられる。

5 - 4

### 設計を意識した 製造技術の研究の必要性

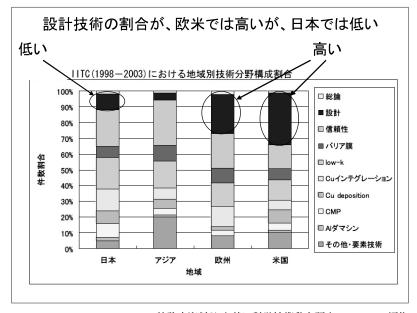

図表7は、配線関係の主要な学会であるIEEE International Interconnect Technology Conference (IITC)での多層配線技術の研究論文状況を地域別に示したものである。欧米では、設計技術を中心に多面的に多層配線技術を捉える研究開発が進んでいることが示されている。これに比較して我が国のこの視点での研究は少ない。

製造技術は、設計技術との依存性を高めることで、より高度な要求に応えられる技術へ進化する。製造技術においても、設計との境界の変化を理解した取り組みが必要である。

### 米国の市販 EDA ツールの支配

現在、市販されている EDA ツールの殆どは米国の EDA ベンダー製のツールである。

現在の我が国の EDA ツール事 情については、次の記述が端的に 状況を表していると思われる。「90 年代に入ってから、日本の産業界 では自社内での EDA 技術の研究 開発をあきらめ、欧米の EDA ベ ンダーのツールを用いて設計を行 っている。短期的に見ると外部か ら導入する方が低コストで設計環 境を整備できる可能性が高い。し かし、長期的・戦略的に考えると、 その"つけ"は大きい。・・・中略・・・ EDA ツールは単なる道具ではな く、その道具を作った人の設計手 法を具現化しているので、その道 具を作った人の設計手法の正しい 理解なくしてその道具のよさを最 大限に引き出すことは難しい。し たがって、我が国の設計力を強化 するためには、EDA 技術の研究 開発を続ける必要があろう。」20) 「設計技術」は、EDA ツールの開 発とその使用上での問題解決活動 の繰り返しで進展する。しかし、 我が国では、企業は、一部を除き 配線設計の EDA ツールの研究開 発をもはや行っていない。理由は、 研究開発に要求される人的パワー が巨大化し、対応ができなくなっ たからである。企業での開発がな くなるにともなって、大学での研 究も極めて少なくなった。この状 態が続いて現在を迎えている。市 販 EDA ツールへの過度の依存は、 「設計技術」の弱体化、無力化を 招く。

市販 EDA ツールに依存する場合でも、単に購入すれば設計ができるほど容易ではなく、設計対象への整合、企業内での設計文化

図表 6 微細化に伴う設計課題の増加

㈱半導体理工学研究センター提供

図表 7 設計を意識した多層配線技術の研究論文状況(地域別)

特許庁資料3)を基に科学技術動向研究センターで編集

を生かした選択が必要になる。優れた市販 EDA ツールの選択には EDA ツールの良否の判定が鍵となる。実際の運用を通した活用の目、継続したベンチマークによる評価の目、開発経験から来る技術の目の養成が重要である。かつて EDA ツールを開発してきた人材が、現在は、市販 EDA ツール選択時の目利きや EDA を教える役割を担っているが、そうした人材さえも減少しており風前の灯の状

態となっている。

配線設計がこれから益々複雑化 してくる状況下で、この状況は危 機的である。

# 5・6 ノウハウの保護について

製造工程での製造装置の使い 方に関して装置レシピ特許という ものがある。半導体製造装置の制 御技術を、従来のような「製造方

法」の特許ではなく、装置レシピ 特許という「物」の特許として権 利を取得する方法であり、使用法 のノウハウに対する強力なガード になる。装置レシピ特許とは、「実 質的には製造装置の制御方法に関 する特許であるが、制御方法の内 容をプログラム又は記憶媒体、記 録媒体という末尾として、制御装 置の制御方法をソフトウエア化し た特許 | である。今、ファンドリ 企業は製造装置の制御方法をソフ トウエア化した装置レシピ特許と して取得することに力を入れてい る。今まで、我が国の半導体デバ イスメーカーは、製造装置の使い

方の法的保護については、無防備に製造装置メーカーに渡しているということはなかったろうか<sup>3)</sup>。

同様なことは EDA ツールの使い方にも当てはまるのではなかろうか。我が国の半導体デバイスメーカー、コンピュータメーカー等の EDA ツールのユーザは、EDA ツールの使い方の法的保護について無防備に EDA ベンダーに渡しているということはなかったろうか。ノウハウを無償で提供していたことはなかったろうか?

EDA ツールの実際の使用面では、様々な使用上のノウハウが要求される。いかなる優れた EDA

ツールであっても未完成であり、この機能不足を補うものがノウハウである。EDAツールに対するEDAベンダーへの問題提起、機能追加要求はEDAツールを育成し、その結果、EDAツールはより良いものになっていくが、その育成されたEDAツールは世界に流通されることになる。この様な形で、無意識のうちにノウハウが流出してしまう。

特に製造関係のノウハウには 機密事項が多く、設計と製造の 融合では一層の法的保護が必要 となる。

# 6

### 今後の対策と提言

前記したように、「配線問題」 の解決に向けては、「製造技術」 と「設計技術」のバランスある 発展が必要になる。今、微細化が 進展し設計に大きな変化が起こっ ている。配線遅延時間を遵守した 「タイミング問題」と製造歩留ま りを考慮した「設計と製造との融 合」がそれであり、共に「配線問 題」に起因するものである。先端 技術の開発には、まさに「すりあ わせ一の技術開発が必要な段階に なってきている。これは世界的な 課題であり、ファブレスとファン ドリ・ビジネスという分業体制で は特に大きな課題になっている。 EDA ツールの進歩は目覚しいが、 この様な設計の複雑化のスピード には追いついてはいない。そのた め、今こそ、我が国の「製造技術」 の強さを生かした「設計技術」を 生み出せるチャンスであるとも言 える。以下では、将来の配線問題 に備えた「設計技術」の強化に向 けた推進策を提言する。

6 - 1

### 配線設計の強化に向けて 核となる EDA ツールの開発 (産官学連携の長期的視点での提言)

上述したように、「タイミング 問題」と「設計と製造との融合」 領域は、本来は、我が国の強さを 発揮できる領域である。もし、核 となる機能部分を自製 EDA ツー ルによって開発できれば、EDA ツールはもとより、開発される LSIの優位性につなげることがで きる。また我が国が強いと言われ ているデジタル情報家電、自動車、 そしてロボットなどの製品におい て、その実現の鍵となる「アナロ グ RF 混載設計」の領域は、EDA ツールが未だ不十分の状態であ る。こうした部分へのいち早い注 力により、LSI 製品の優位性も確 保できるだろう。自製 EDA ツー ル開発を通して、設計ノウハウと 技術力の蓄積、継承、そして保護 を行うべきである。以下にその具 体的推進方法を述べる。

### (1)「製造技術」を活かす先行的な 設計手法と EDA ツールの開発

先端技術開発へ向けた製造技術 との「すりあわせ」での設計技術 の開発では、まず、設計手法の開 発が重要であるが、設計手法の開 発のためには遵守すべき設計ルー ルの決定が必要である。そこでは、 設計と製造が共に歩み寄った設計 ルールの設定が必要であり、いた ずらに他方へ制約を強いるもので あってはならない。そのためには、 設計ルール採用による投資効果を 定量的に把握できることが必要に なる。すなわち、どのような配線 パターン制約が、歩留まりやタイ ミングへどのように影響するか、 という効果の把握である。ここが 不明確のままでは、設計と製造の 融合は掛け声だけに終わる。設計 手法は設計フローとして具現化さ れ、その設計フローを最適に実現 する EDA ツールの要求仕様が決 定され、自製 EDA ツールの開発 へとつながっていく。既存の市販EDAツールへの依存だけではこの様な設計手法の構築は難しい。3章では配線技術研究の新しい動きを述べたが、こうした最先端の研究開発を遅滞なく進めるためには、新しい設計手法とEDAツールのタイムリーな先行開発を進めるべきであろう。また製品優位性を確保できる領域を見極め、それに向けて先行したEDAツールの研究開発が有効である。

なお、ここでは「設計技術」の中で「配線問題」に直接関係する配線設計に焦点をあてたが、システム設計、論理設計、テスト設計は、設計生産性、設計品質の向上に重要な役割を果たすため、それらの基盤たるEDAツールに対しても強化が必要と考えられる。

### (2)異研究領域のコラボレーション

EDAツールの開発にあたっては、設計と製造の知識、微細化の進展で接近しつつある物理限界への対応としての物理法則や原理などの基本的な知識などが求められる。専門化が進んだ現状では、これをすべて一個人に求めるのは難しい。そのため、異研究領域のコラボレーションが重要になる。設計・製造を関メーカーも含めた連携と情報共有も必要である。製造装置メーカーからの課題解決提案を、EDAツールへ反映できれば、大きな発展が望めるだろう。

また、シリコンとナノテクノロジーの研究者によるコラボレーションも必要になる。例えば、配線設計の事例ではないが、高・低誘電体材料の解析への計算科学技術の研究 21、22)やプロセス開発の基盤としての TCAD(Technology Computer Aided Design)も進化

している。微細化は既にナノの領域に突入しており、今まで分離していたこうした技術領域が接近しつつあり、これらが重なる領域には革新的な LSI 開発環境の実現も考えられる。異研究領域のコラボレーションは、積極的に推し進めていく必要がある。

### (3)開発推進に向けた体制作り

この分野は、企業での実際の 設計・製造現場での意見の反映無 しには具体的な成果は期待できな い。そのため、開発の推進体制は 企業主体のコンソーシアム形式に ならざるを得ないだろう。大学の 研究者には、このようなコンソー シアムへ積極的に参画し、科学的 知見と理論面からの貢献を期待し たい。コンソーシアムの成果は、 メンバー企業が持ち帰り、各企業 の個別要件を追加して活用するこ とになろう。企業間協業でのノウ ハウの共有化については、メンバ 一企業内に閉じるもの、公開して 広く標準化を狙うものなど委員会 を設置し協議して決めていくのが 望ましい。

企業と大学の協力体制の推進で は、大学の研究者へのモチベーシ ョン向上が課題となる。研究の中 には企業秘密として開示不可を選 択する場合もあり、大学で評価さ れる論文数には貢献できない場合 も生じうる。モチベーションの向 上に向け、論文、特許以外の評価 (例えば、産学連携による研究資 金調達額など)の設定も必要とな ろう。しかしながら、世界に目を 向ければ、既に多くの大学の研究 者が設計の分野で活躍し、多くの 論文が大学から発表されていると いう事実があり、このような問題 が我が国で解決できない訳はなか ろう。

#### 6 - 2

### 「製造技術」と「設計技術」 のバランスある先端化にむけて

### (1)積極的な知財活動の推進 (産業界に向けた 短期的視点での提言)

「設計と製造の融合」という領 域では、製造で生じる欠陥(ゴミ による欠陥、プロセス欠陥、リソ グラフィ欠陥、ランダム欠陥など) を、設計のどの段階(論理設計、 配線設計など)で盛り込むかによ って、解決法に複数の組み合わせ が考えられる。この解決法は、歩 留まりに直接影響するため、ビジ ネスに直結する知財価値の高いも のである。ここでは、特許か、企 業秘密かを区分けした知財方針の 選択が重要である。配線パターン のように目で見えて侵害判定が容 易なものは特許に、製造歩留まり に関係する情報や解析手法などは 侵害判定不能のため企業秘密にす る、といった区分けを明確に行な うことである。企業秘密とする場 合には、門外不出を確実に行える セキュリティシステムの完備も必 須になる。

実は、設計ノウハウの保護は、6・1で述べたような自製 EDA ツールの開発だけでは解決しない。実際の設計現場では、市と、核となる機能部分の自製 EDA ツール化の併用による LSI 設計フローが構築され、運用されるだろう からである。市販 EDA ツールを活用する場合には、ノウハウの価値を意識し、これを積極的に保護する方策を採るべきである。 EDA ツール使用にかかわるパラメータ設定や使用法を、装置レシピ特計のようにプログラム化し、「物」

として管理することも検討すべき である。そして、侵害判定の容易 化を意識したグラフィカル・ユー ザ・インターフェースを取入れる ことなどの工夫が必要となろう。 このように、ユーザとしての立場 も生かし、ノウハウの戦略的活用 を図るべきである。

### (2)ターゲットの明確化

### (政府が行なうべき中長期的施策)

術を生かした応用開発を企業で行うというサイクルを目指すべきであろう。

現在、高速化と低消費電力化は 別課題として捉えられており、特 に、情報家電向けの低消費電力 化に力点が置かれている。しか し、本来、将来の LSI は高速化と 低消費電力化は別問題ではありえ ない。高速化への対応も必要であ る。例えば、携帯電話では多機能 化の進展に伴い、高性能化の追求 も盛んに行われている。また、自 動車では半導体部品の採用が急激 に進展しており、自動車用部品で は、厳しい環境条件下での高性能 化への要求が非常に高くなってい る<sup>23)</sup>。現在、NEDO などから示 されているロードマップは低消費 電力 LSI に向いているが 24)、高性 能化を視野にしたロードマップ作 成にも期待したい。

高速化への対応として、今後 のスーパーコンピュータで用い られる高速 CPU をターゲットにした「製造技術」と「設計技術」と「設計技術」を開発していくことは、Pre-Competitive な研究領域におけるベクトル合わせという意味でひとつの候補と考えられる。過去に中の人間と考えられる。過去に中の大端技術が追求され、その成果が高用システムや CMOS LSI の開発に使われた経緯がある。EDAツールについても、タイミング問題への対応など今日の微細化で直面している問題に対して、スーパーコンピュータ設計で生まれた技術が多く生きている。

また、アナログRF混載設計領域をターゲットにした「製造技術」と「設計技術」を開発していくこともベクトル合わせの候補になりうる。ここでは、厳しい電力制限のもとでの高性能化の追及を特徴としており、極めて高度な技術が要求される。

# 7

### おわりに

ここでは、シリコンエレクト ロニクス領域での具体問題として LSIの「配線問題」を取り上げ、 配線問題の改善に大きく影響す る配線設計の課題を明確化し、将 来の配線問題に備えた設計技術の 強化の必要性を述べ、その推進策 を提言した。この領域はシリコン エレクトロニクスでの我が国の研 究水準を復活上昇させるポテンシ ャルを持つと考えられる。特に、 EDA ツールにはノウハウが集約 されるため、EDA ツールの技術 開発は重要であり、LSI 開発力の 強化に向けて必須の研究開発課題 である。

### 謝辞

本稿の執筆にあたって、広島 大学 ナノデバイス・システム研 究センター 岩田 穆センター長、 東京工業大学統合研究院 益一哉 教授、東京工業大学精密工学研究 所 大嶋洋一客員教授、京都大学 大学院 情報学研究科通信情報シ ステム専攻 小野寺秀俊教授、中 央大学 理工学部 電気電子情報通 信工学科 築山修治教授、㈱半導 体理工学研究センター (STARC) 下東勝博社長、同研究推進部 平田雅規上級研究員、㈱東芝研 究開発センター 先端機能材料ラ ボラトリー 伊藤聡研究主幹、同 LSI 基盤技術ラボラトリー 加藤 弘一研究主幹、日本電気㈱コン ピュータ事業部 片桐勝 LSI 技術 エキスパート、独新エネルギー・ 産業技術総合開発機構 電子・情 報技術開発部 五十嵐泰史主査ほ かの皆様から、ご意見、資料の提 供などのご協力を頂きました。こ こに関係の皆様に厚く御礼申し上 げます。

#### 参考文献

- 1) http://www.nistep.go.jp/

achiev/ftx/jpn/rep097j/pdf/

rep097j07.pdf

- International Technology Roadmap For Semiconductors

Edition Interconnect

- 3) 平成 15 年度特許出願技術動向調 査報告書 LSI の多層配線技術 (特許庁、平成 16 年 3 月)

- 4) LSI 配線の解析と合成 ディープ サブミクロン世代の LSI 設計技 術 (C. チェン他、小野寺秀俊監訳、 培風館)

- 5) SiCMOS オンチップ伝送線路配線(益一哉、2005 年電子情報通信学会エレクトロニクスソサイエティ大会)

- 6) オンチップ伝送線路配線による

- 回路性能向上予測(上薗他、DA シンポジウム 2005)

- 7) 脳型情報処理システムのための 視覚情報処理プロセッサの開発: http://jstore.jst.go.jp/ image/research/pdf/R03/ R030000146.pdf (小柳光正)

- 8) A 3 D Integration Scheme utilizing Wireless Interconnections for Implementing Hyper Brains (A.Iwata他 ISSCC 2005.2)

- 9) A 0.95mW/1.0Gbps Spiral-Inductor Based Wireless Chip-Interconnect with Asynchronous Communication Scheme (M.Sasaki他 Symposia on VLSI Technology and Circuits 2005.6)

- 10) A 195Gb/s 1.2W 3D-Stacked Inductive Inter-Chip Wireless Superconnect with Transmit Power Control Scheme(N.Miura 他 ISSCC 2005.2)

- 11) エレクトロニクスの限界を打破 する Si ナノフォトニクス (大橋 啓 之、NEC HPC 研 究 会、2005 年 7 月)

- 12) http://www.intel.co.jp/jp/intel/pr/press2005/050217.htm

- 13) http://fcrp.src.org/member/ centers/int/about.asp

- 14) SEMATECH's Idea-to-Market Strategy (A. Oscilowski The Second Annual IP Innovation Symposium 2005.11)

- 15) http://www.nedo.go.jp/informations/koubo/171013\_1/171013\_1.html

- 16) http://www.nedo.go.jp/ nedopost/h18\_3/data/18np3-ele1a.pdf

- 17) 2.16 GHz SPARC64 マイクロプロセッサ設計用タイミング・レイアウト設計手法(伊藤則之他、DA シンポジウム 2005)

- 18) 半導体 LSI のできるまで (日刊 工業新聞社)

- 19) 設計から見た DFM に関する提言(下東勝博 半導体界面制御技術第 154 委員会、第 51 回研究会資料、2005 年 10 月)

- 20) システム LSI 開発の現状と課題 (2005 システム LSI 技術大全、電 子ジャーナル p. 32)

- 21) 第一原理計算による High k 膜 解析 (2005 年半導体 MIRAI プロ ジェクト成果報告会資料 p.142、 2005 年 10 月)

- 22) 計算材料科学によるナノ材料設 計と産業応用(物質・材料研、 大野隆央、計算科学技術シンポ ジウム、2005年9月)

- 23) 自動車がマイコンやセンサーの 塊に ハイブリッド化が車デバ イスの進化を促進(藤川東馬、 日経マイクロデバイス創刊 20 周 年 特別編集編、2005 年 10 月)

- 24) 電子・情報分野の技術ロードマップ (独 新エネルギー・産業技 術総合開発機構、2005 年 4 月)

#### 執筆者

野村 稔 科学技術動向研究センター http://www.nistep.go.jp/index-j.html

情報・通信コーット

企業にてコンピュータ設計用 CAD の研究 開発、ハイ・パーフォーマンス・コンピュ ーティング領域、ユビキタス領域のビジネ ス開発に従事後、現職。スーパーコンピュ ータ、LSI 設計技術等、情報通信分野での 科学技術動向に興味を持つ。

### ■略語のフルスペル■ -

CMOS: Complementary Metal-oxide Semiconductor

**DRAM**: Dynamic Random Access Memory

DRC: Design Rule Check

**EDA**: Electronic Design Automation **OPC**: Optical Proximity Correction

RF: Radio Frequency

**SEMATECH**: Semiconductor Manufacturing Technology Institute