# 特集[2]

# LSI技術の研究動向

―VLSI シンポジウムと シリコンナノエレクトロニクスワークショップの発表より― 情報通信ユニット 山崎 哲也

# はじめに

LSI技術の重要な国際会議に数えられる VLSI シンポジウム (VLSI Symposia on Technology and Circuits) とシリコン ナノエレクトロニクス ワークショップ (以下ナノエレクトロニクスワークショップ)が、今年も6月中旬に米国ハワイで開催された。これらの会議はIEEE主催で毎年日本と米国で交代で開かれている。VLSIシンポジウムはデバイス技術に関するシンポジウム オンVLSIテクノロジー (以下テクノ

ロジーシンポジウム)と、回路技術に関するシンポジウム オン VLSIサーキット(以下サーキットシンポジウム)から構成される。いずれも現在生産に使われている最先端技術から1~2世代先(今年の場合は130nm~65nmの世代)を目指して開発中の技術を対象にしている。発表の中心となるのは企業である。今年はテクノロジーシンポジウム86件(内2件は基調講演)、サーキットシンポジウム88件(内4件は基調講演)の 発表があった。参加者は両方合わせて約600名。

ナノエレクトロニクスワークショップはさらに先の将来技術が中心となる。今後のLSI技術の方向性を占う点では重要な会議である。発表の中心となるのは大学である。56件の発表(内招待論文6、ポスター27)があり、参加者は約200名。

ここでは、これらの国際会議から、トピックスを紹介する。

# 今年の傾向

## VLSI シンポジウム

## (1)テクノロジーシンポジウム

単純なスケーリング(デバイス 構造を微細化して、集積度と動作 速度を向上する) が限界に近づい ていることが以前から指摘されて いる。この限界を破るために高誘 電率(High-k)ゲート絶縁膜<sup>①</sup>や 低誘電率(Low-k)絶縁膜<sup>②</sup>、SOI (シリコン オン インシュレー ター) ③といった新デバイス構造 が注目され、一部はすでに実用化 されている。今年は特にHigh-kゲ ート絶縁膜に関連して16件の発 表があった。材料としては直近で は窒酸化シリコン (SiON)、65nm 世代以降をでは酸化ハフニウム (HfO<sub>2</sub>) が有力候補であり、この2 つに関する発表が多い。ただし、トランジスタの動作速度に直結するキャリア移動度が、従来のSiO<sub>2</sub> ゲート絶縁膜に比べて低下するというHigh-kゲート絶縁膜共通の問題についてはまだ解決のめどがなく、実用化へむけて大きな壁となっている。

また去年のナノエレクトロニクスWSで注目を集めた歪みSi構造(科学技術動向2001年7月号および2002年1月号参照)に関するセッションが今年から新設され、4件の発表があった。他にハイライトセッションにおいてIBMがHigh-kゲート絶縁膜と歪みSi構造を使ったデバイスの発表を行っている(歪みSi構造についてはトピックス参照)。

もうひとつの特徴として、携帯

機器の普及と高性能化や無線LANの市場が広がり始めたことを反映して、プロセッサとメモリ、アナログ回路などを1チップに集積するSoC(システム オン チップ)、それに関するメモリ、アナログデバイス、高周波デバイスに関する発表に注目が集まった。その分、単体のDRAMの発表は参加者が少なく、テクノロジドライバとしてのDRAMの地位が低下している事が伺われた。

微細化の決め手となる次世代露 光技術 $^{\oplus}$ については $F_2{}^{\oplus}$ 、EPL (電子線投影露光) $^{\oplus}$ について発表 があったが、65nm世代(2007年 ごろから量産)に装置、マスク、 プロセスの開発が間に合うか疑問 がもたれている。そのため、130~ 100nmで使用した  $ArF{}^{\oplus}$ を 65nm 世代に延命するマスク技術 の発表が注目された。これについ ては次章で述べる。

### (2)サーキットシンポジウム

ここでもSoCに関連する発表が注目を集めていた。また、不揮発性メモリに関して、現在主流であるフラッシュメモリの多値化技術(1メモリに2ビット以上の信号を記録する)や、次世代メモリ®である磁気メモリ(MRAM)®、強誘電体メモリ(FeRAM)®の発表が注目を集めていた。

他に注目を集めたのが省電力技 術である。携帯機器や家電におい ては重要な性能指標のひとつであ

り、PC用プロセッサのような高 性能デバイスでも高集積化と高速 化に伴い増加する熱の問題は深刻 になりつつある。この問題につい てのパネルディスカッションでは 活発な議論が行われた。パネルデ ィスカッションでNECの水野氏 は、チップあたりの発熱量が限定 されるため、性能向上の速度が現 在の一世代に3倍から半分程度に 低下するとした。パッケージやト ランジスタ設計、冷却方法などの 対応策が出されたが、決め手とな るものはでなかった。日立の伊藤 氏はメモリ技術をベースにしたプ ロセッサのような、新しい発想が 必要であるとしている。

基調講演ではテクノロジーシン ポジウム、サーキットシンポジウ ムともにMEMS<sup>⑥</sup>が取り上げられ た。テクノロジーシンポジウムで は東北大学の江差氏が、サーキッ トシンポジウムではミシガン大学 の K. D. Wise 氏がそれぞれ発表し たが、特に後者は人体に埋め込む インプラント治療装置への応用を 示した。センサと薬などの投与装 置、コントローラを組み合わせた もので、大きさは0.5mm以下、 体外から電波によって電力を供給 する。神経への電気刺激によって 筋肉を制御することも可能で、パ ーキンソン氏病などの神経性難病 患者への応用が研究されている。

## 用語説明 -

#### ①高誘電率(High-k)ゲート絶縁膜

現在トランジスタの主流となっているFET(電界効果ト ランジスタ)ではソース・ドレインと呼ぶ2個の電極の間に チャネル領域をもうけ、ここにゲート絶縁膜を挟んでゲー ト電極から電圧をかけることでチャネル領域に電荷を発生 させ、ソース・ドレイン間に電流を流す。ゲート電極、ゲ ート絶縁膜、チャネルがそれぞれ金属、酸化物、半導体と なっているのがMOS (Metal-Oxide Semiconductor) FET で代表的な半導体デバイスの一つである。チャネルがp型 半導体かn型半導体かでそれぞれpMOS、nMOSと呼ばれ、 この二つを使って論理回路を形成するのがCMOS(相補型 MOS)。MOSFETが微細化するとチャネルも小さくなるた め、十分なオン電流を得るためにはゲート絶縁膜を薄くし てチャネルに多くの電荷を発生させる必要がある。しかし、 現在のゲート絶縁膜であるSiO2は、その膜厚が1nmを切 るようになると膜の欠陥やトンネリングによるゲート漏れ 電流が増加する。そこで、十分な電荷をチャネルに発生さ せることができ、漏れ電流も低減できるゲート絶縁膜とし て、SiONやHfO2などの高誘電率材料の使用が研究されて いる。

### ②低誘電率(Low-k)絶縁膜

LSIの高速化に伴い、信号が配線を進む時間も問題となってきた。そこで、信号の伝播速度を上げるため、配線周りの絶縁膜に、現在のSiO<sub>2</sub>に代えて低誘電率の絶縁膜を使用することが検討されている。現在有機化合物材料や多孔質材料が研究されている。

#### **3** SOI

通常のSiウエハ上にLSIを形成すると、ウエハ自体に導電性があるため、余分な電力消費や速度低下を引き起こす。そこで、ガラスなどの絶縁基板に薄い( $0.5\sim100~\mu$  m)ウエハを張り付けたり、ウエハ内部に酸化シリコンの絶縁層を形成してウエハの影響を排除したのがSOI(Silicon on Insulater)。

#### 4次世代露光技術

現在、アルゴン・フッ素(ArF)ガスを使用したエキシマーレーザー(波長193nm)が露光機の光源に使用されている。65nm世代以降の次世代露光機には、解像度を上げるため、より短い波長の光を出す光源が使用される。現在、ArFにかえてフッ素( $F_2$ )ガスを用いる $F_2$ エキシマーレーザ(波長153nm)、金属ガスプラズマを使用するEUV(波長13nm)、電子線を使ってマスク投影露光をするEPL(波長は可変)が有力候補として上げられる。いずれも一長一短があるが、 $F_2$ が最有力候補であった。この他にX線露光機(現在、開発はほぼ中断)、LEEPLE(縮小投影のEPLと違い、等倍コンタクトマスクを使う電子線露光機、日本のベンチャーが開発し、NTTやソニーが後援している)がある。

#### ⑤次世代メモリ

現在のメモリは、高速でプロセッサ内やキャッシュメモリに使用されるSRAM(スタティックランダムアクセスメモリ)、比較的高速で高集積化できメインメモリとして使用されるDRAM(ダイナミックRAM)、書き込み・消去がやや低速だが不揮発性(電源を切っても記憶が残る)のフラッシュメモリ、低速だが容量の大きいハードディスクや光ディスクという階層になっている。次世代メモリにはDRAM以降を置き換える不揮発性で高速、低消費電力のメモリが求められる。磁気メモリ(MRAM)はハードディスクと同様に磁気によって記憶を行うもの。強誘電体メモリは電圧によって誘起された電荷が電圧を切っても残る強誘電体の性質を使ったメモリ。他に結晶状態とアモルファス状態で電気抵抗が変わる相変化物質を使うOUM(Intelが後援するベンチャーOvonyx社が開発中)もある。

#### **6 MEMS**

Micro-Electro-Mechanical Systems。半導体製造技術をベースにした微細加工技術を使い数百点から数点の可動部を持つ微細な電気機械システム。マイクロマシンとも言われる。

## ナノエレクトロニクス ワークショップ

歪みSi構造に続く将来技術として今年のナノエレクトロニクスワークショップで中心となったのはFinFET構造という、立体構造を

もつトランジスタである。これについては「次のデバイス構造―FinFET―」の章で詳しく述べる。ナノテクノロジーに分類される技術では、、量子ドットなど、デバイスとして実現性が高い構造を使った発表が目立った。一方、カーボンナノチューブトランジスタ

についてはIBMの招待講演のみであった。これらのナノデバイスのほとんどは極低温でないと動作しないため、どうやって室温動作可能なナノデバイスを設計するかと言う点に議論が集まった。この点が解決されるにはまだ時間がかかりそうである。

## 次世代露光技術

微細化の決め手となる露光技術について現在のロードマップ(図表1)では65nm世代が $F_2$ 、それ以降が電子線投影露光(EPL)または極紫外線露光<sup>④</sup>(EUV)となっている。しかし、 $F_2$ 露光装置が65nm世代のみとなりそうなことや技術的困難さからIntelなど欧米半導体各社がEUVへ傾きつつある(科学技術動向2001年4月号)。このような動きは日本の半導体会社にも影響を与えているようである。

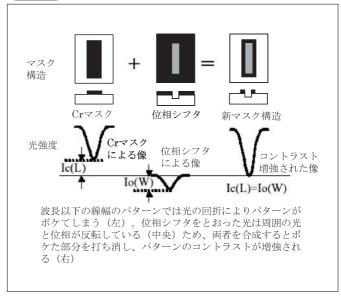

今回Selete®はF₂用レジストの開発が進んでいることを示したが。その一方、松下は65nm世代の露光技術としてArF、F₂、EPLを比較し、焦点深度と解像度の兼ね合いからEPLが最適とした。松下は同時に、130~100nmで使用したArFを65nm世代に延命するためのマスク技術の発表も行っており、注目を集めた(図表1)。これは配線パターンの中央に1/2波長位相をずらす位相シフト部分を設け、周囲の光と干渉させるコントラスト増強技術の一種で、ArF

### 図表 1 ITRS2001 における LSI 寸法と露光技術のロードマップ

|                          | 2001 | 2002 | 2003 | 2004 | 2005                                                                     | 2006 | 2007 | 2010 |

|--------------------------|------|------|------|------|--------------------------------------------------------------------------|------|------|------|

| DRAM 1/2 pitch           | 130  | 115  | 100  | 90   | 80                                                                       | 70   | 65   | 45   |

| MPU 1/2 pitch            | 150  | 130  | 107  | 90   | 80                                                                       | 70   | 65   | 45   |

| MPU Physical Gate Length | 65   | 53   | 45   | 37   | 32                                                                       | 28   | 25   | 18   |

| 露光技術                     | ArF  |      |      |      | $F_2$ $\left\langle egin{array}{c} EPL \\ EUV \end{array} \right\rangle$ |      |      |      |

(単位: nm)

ITRS2001(International Technology Roadmap for Semiconductors 2001年度版)等から科学技術動向研究センター作成

## 図表 2 松下が発表したコントラスト増強技術

A. Mikasa 他 2002 Symphosium on VLSI Technology DIget of Technical Papers p.200(2002 年)等から科学技術動向研究センター作成

### 用語説明

#### (7) Selete

半導体先端テクノロジーズ。日本の半導体会社が中心になって1996年に設立した共同研究組合。当初は300mmウエハ対応の装置評価や標準化を行っていたが、現在は65nm以降の半導体製造技術の研究を行っている。

#### **®ASET**

超先端電子技術開発機構。日本の半導体産業関連企業十数社が集まって構成する半導体技術の共同研究組合。 MIRAIはASETが行っている65nm世代の技術開発プロジ

エクト。

#### ⑨フッ化カルシウムレンズ

波長の短いF<sub>2</sub>エキシマーレーザではレンズ素材として通常のガラスや石英が使えないため、フッ化カルシウム (CaF<sub>2</sub>、蛍石とも言う)のレンズを用いる。しかし、フッ化カルシウムには複屈折 (結晶方位によって屈折率が異なる性質、レンズには都合が悪い)の問題や、機械的強度が弱く、自重でレンズが変形するなどの問題があった。

露光機を使っても65nm世代に必要な焦点深度と解像度が確保できるとしている。また、従来の位相シフトマスクが繰り返しパターンでないと適用できなかった(隣り合うパターンの位相を反転し、その干渉でコントラストを増強する)のに対し、孤立パターンに適用できる点も注目される。

F<sub>2</sub>露光技術に関しては、同じ6

月にASET®が研究成果発表を行っており、レーザやマスク材料、レジストの開発は進んでいるものの、フッ化カルシウムレンズ®の量産、マスクを保護するペリクル材料、汚染物質の焼き付きなどに対する長期的耐久性にまだ問題があるとしている。それ以外のEPL、EUVも装置、マスク、プロセスの開発が間に合うか現時点では不

透明であり、増加する投資を低減する点でもArFの延命が有力な選択肢となりつつある。なお、日本でも45nm世代以降でのEUV実用化を目標にした極端紫外線露光システム技術開発機構(EUVA)を、露光機メーカーほか10社が今年5月に立ち上げている。

## 次のデバイス構造 ―FinFET-

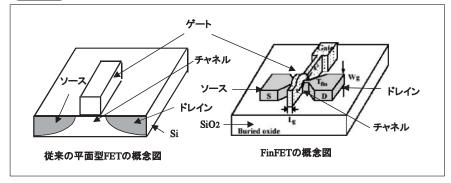

歪みSi構造に続く次世代技術と して今年の中心となったのはFin-FET構造である。これは、細く フィンのように形成したチャネル (トランジスタで電流が通る部分) の周りにゲート電極を置く立体構 造である(図表3)。現在の平面構 造トランジスタに対し、動作速度 向上、オン電流向上と漏れ電流低 減(消費電力低減)が期待できる。 またFinFETはプロセスの工夫に よりリソグラフィーの加工限界寸 法より微細なトランジスタを作る ことが可能である。招待講演を行 った台湾 TSMC社の C. Hu(Fin-FETの発明者でUCバークレー教 授でもある) は、TSMCで試作し たFinFETの特性を示した後、現 在IBM,モトローラ、AMD等が同 様の構造を研究しており、2010年 以降のトランジスタ構造の有力候 補であると述べた。

TSMCはVLSIシンポジウムで

## 図表 3 FinFET と従来の平面型 FET

R. Yang 他 2002 Symphosium on VLSI Technology DIget of Technical Papers p.104(2002年)等から科学技術動向研究センター作成

ゲート長35nm (65nm 世代に相当) のFinFET の詳しい発表も行っている。それによると、High-kゲート 絶縁膜などの新材料を導入しなくても、充分な性能を発揮できるとのことである。また、モトローラも本ワークショップでFinFET の基本特性に対する発表を行っている。

ただしチャネルが細いため、電流量がとれない問題があるが、上記のHu氏は複数のチャネルを一

つのトランジスタに形成すること で電流量を上げる構造を示した。

一方、従来の平面型FETにおいて、ゲート面の凹凸が電荷の移動を攪乱し、FETの性能を低下させるという発表が今回数件あった。エッチングでフィンを形成するFinFET構造ではゲート面の凹凸は平面型FETより大きくなることが予想される。この点が今後の課題となる可能性もある。

# 各国の研究開発動向

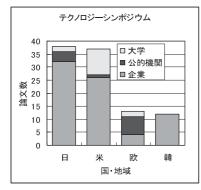

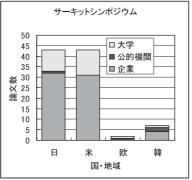

最後に各会議での論文数からみた各国の研究開発動向を簡単に分析する。図表4に各会議の国・地域別論文数を示す。ここでは招待講演、基調講演、ポスターセッションを含めるが、パネルディスカッションのパネラーは含めていない。両シンポジウムでは日・米がほぼ同数であり、最近の国際市場で日本半導体産業のシェアが低下し

ていること、米国での開催であることを考えると健闘していると言っていいであろう。また、韓国が欧州を押さえて3位となり、台湾も存在感を増してきている。なお、サーキットシンポジウムのその他3論文はカナダの大学で、回路技術では一定の地位を占めている。

一方、ナノエレクトロニクスワ ークショップでは他に比べて日本 の論文数が少ない。これは日米交代で開催されるため、日米の論文数が開催国かどうかで極端に増減するという、この会議特有の傾向のためである。他方、韓国が日本、欧州を押さえて2位となっており、将来技術に関する研究も活発になっていることが伺える。参考までに日本開催であった2001年のこの会議の国・地域別発表論文

数を図表4に追加しておく。

各会議における主要4カ国・地域の発表機関別論文数を図表5に示す。ここで、日本のSeleteや欧州のIMEC®などの複数企業による共同研究組織は公的機関に分類している。

両シンポジウムが企業中心、ナ ノエレクトロニクスワークショッ プが大学中心という傾向がはっき りでている。

サーキットシンポジウムで日本 の大学が健闘していることがわか る。一方、テクノロジーシンポジ ウムでは日本の大学の発表がわず か実質1件(2件中1件は基調講 演)しかない。米国での開催とい うこともあるが、最先端デバイス の研究に必要な設備を持つ大学が 少ないのもその原因の一つであろ う。実際、米国の大学の発表数が 多いのもテキサス大学など設備を 持つごく少数の大学が複数の発表 を行っているためである。なお、 欧州の公的機関の割合が多いのは、 IMEC およびフランスの CEA <sup>®</sup>が 共同研究などの形で発表を行って

### 図表 4 国・地域別論文数

| 国• | ·地域 | テクノロジー<br>シンポジウム | サーキット<br>シンポジウム | ナノ<br>エレクトロニクス<br>ワークショップ | 2001年Siナノ<br>エレクトロニクス<br>ワークショップ |

|----|-----|------------------|-----------------|---------------------------|----------------------------------|

| 日  | 本   | 35               | 37              | 8                         | 18                               |

| 米  | 国   | 32               | 42              | 25                        | 6                                |

| 欧  | 州   | 8                | 2               | 9                         | 7                                |

| 韓  | 国   | 12               | 5               | 10                        | 5                                |

| 台  | 湾   | 4                | 2               | 2                         | 0                                |

| 中  | 国   | 0                | 2               | 0                         | 0                                |

| 1  | 他   | 1                | 3               | 0                         | 0                                |

\*共同発表による重複あり 各学会のプロシーディングより科学技術動向研究センター作成

いるためである。

ナノエレクトロニクスワークショップでは韓国の公的機関の割合が多いことが目立つ。特にISRC (Inter-University Semiconductor Research Center)と Seoul National Universityの組み合わせで多くの発表をしている。02年の韓国論文数10件のうち7件が上記の組み

合わせである。ISRCは1989年に Seoul National University内に開設された大学共有の半導体研究施設で、同時に産学の共同研究センターとしても機能している。今後ISRCが多くの大学に使われるようになればさらに韓国の論文数が増えるかもしれない。

## 用語説明

#### 10 IMEC

ベルギー王国のフランダース州政府、州内の4大学及び半導体関連企業が共同運営する産学官半導体研究センター。

①CEA フランス原子力公社

#### 図表5)各会議の発表機関別論文数

35

30

25

10

0

無 20 禁 15

# 終わりに

今回の会議を通して、65nm以降に向けて個々の技術は確実に進歩している。また、たとえば露光装置のように複数の選択肢がある技術も主流となる技術がだんだん明らかになっている。ただし、ま

だ本命を決定するまでには達していないようである。ロードマップ通り2007年に65nm世代の生産を開始するには後2年程度で使用する技術を決定しないと、LSI設計と製造ラインの構築が間に合わな

くなるおそれがある。

ナノエレクトロニクスワークショップ

口大学

□企業

■公的機関

国別の論分数を見ると、韓国、 台湾からの発表が増加している。 今後、中国からの発表の増加も予 想され、アジアの存在感がさらに 増すものと思われる。